# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note: Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

# MITSUBISHI 8-BIT SINGLE-CHIP MICROCOMPUTER 740 FAMILY / 38000 SERIES

| 1/ / /      |           |      |       |        |      |            |   |

|-------------|-----------|------|-------|--------|------|------------|---|

| Keep safety | / tiret i | ın ۱ | /OLIF | CITCLI | it c | IDRIANCI   | ı |

| Troop salet | y iii St  |      | y Oui | CIICUI |      | icoldi lo: |   |

• Mitsubishi Electric Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of non-flammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Mitsubishi semiconductor product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Mitsubishi Electric Corporation or a third party.

- Mitsubishi Electric Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts or circuit application examples contained in these materials.

- All information contained in these materials, including product data, diagrams and charts, represent information on products at the time of publication of these materials, and are subject to change by Mitsubishi Electric Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for the latest product information before purchasing a product listed herein.

- Mitsubishi Electric Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- The prior written approval of Mitsubishi Electric Corporation is necessary to reprint or reproduce in whole or in part these materials.

- If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for further details on these materials or the products contained therein.

# REVISION DESCRIPTION LIST

# 3820 GROUP USER'S MANUAL

| Rev. | Revision Description | Rev.   |

|------|----------------------|--------|

| No.  | Revision Description | date   |

| 1.0  | First Edition        | 970901 |

|      | EOL announced        |        |

# **Preface**

This user's manual describes Mitsubishi's CMOS 8-bit microcomputers 3820 Group.

After reading this manual, the user should have a through knowledge of the functions and features of the 3820 Group, and should be able to fully utilize the product. The manual starts with specifications and ends with application examples.

For details of software, refer to the "SERIES 740 <SOFTWARE> USER'S MANUAL."

#### **BEFORE USING THIS USER'S MANUAL**

This user's manual consists of the following three chapters. Refer to the chapter appropriate to your conditions, such as hardware design or software development.

#### 1. Organization

#### CHAPTER 1 HARDWARE

This chapter describes features of the microcomputer, operation of each peripheral function and electric characteristics.

#### CHAPTER 2 APPLICATION

This chapter describes usage and application examples of peripheral functions, based mainly on setting examples of related registers.

#### CHAPTER 3 APPENDIX

This chapter includes precautions for systems development using the microcomputer, a list of control registers, the masking confirmation forms (mask ROM version), ROM programming confirmation forms (One Time PROM version) and mark specification forms which are to be submitted when ordering.

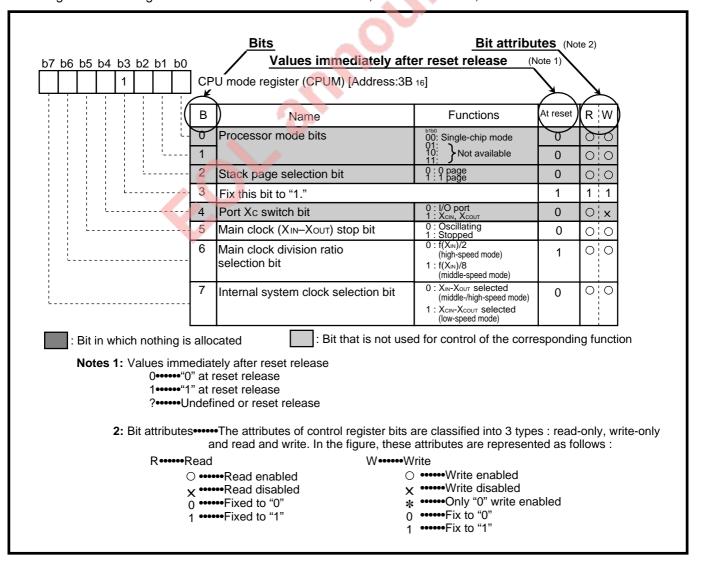

#### 2. Structure of register

The figure of each register structure describes its functions, contents at reset, and attributes as follows:

# **Table of contents**

### **CHAPTER 1. HARDWARE**

| DESCRIPTION                           |                                   | 1-2 |

|---------------------------------------|-----------------------------------|-----|

| FEATURES                              |                                   | 1-2 |

|                                       |                                   |     |

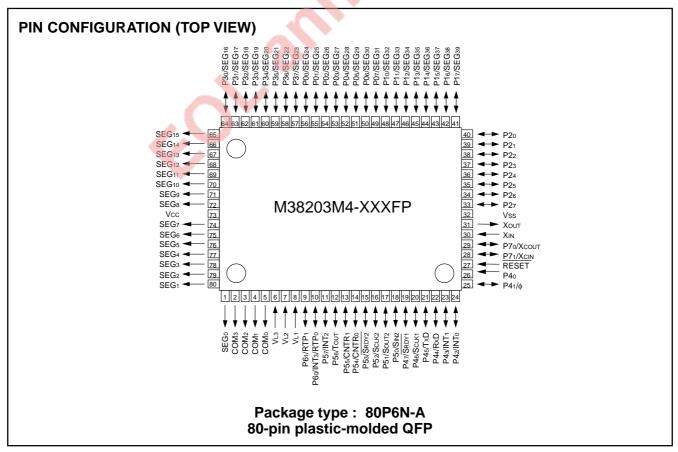

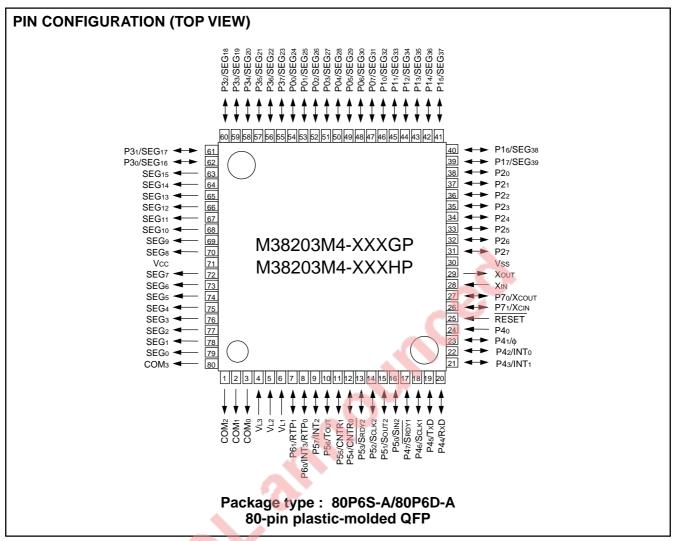

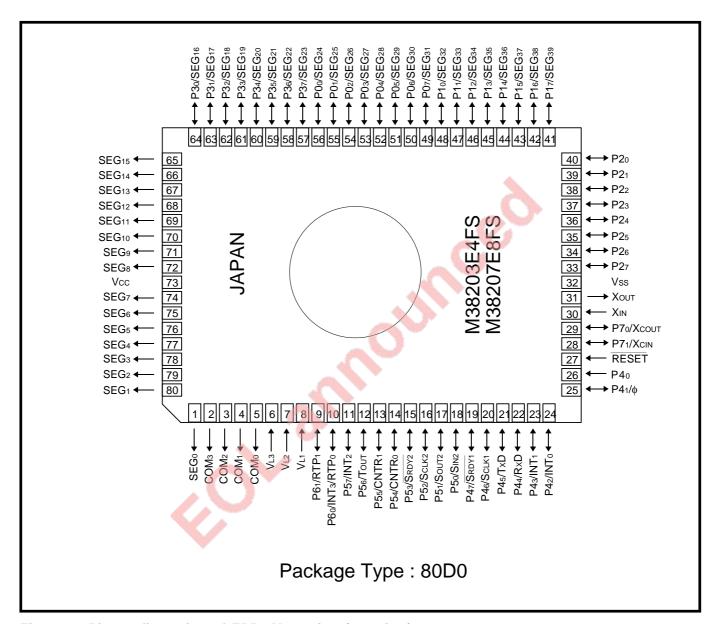

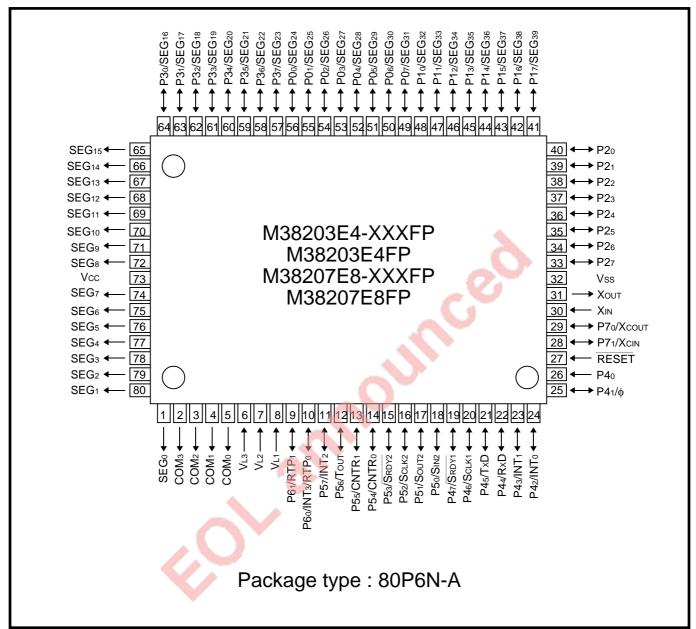

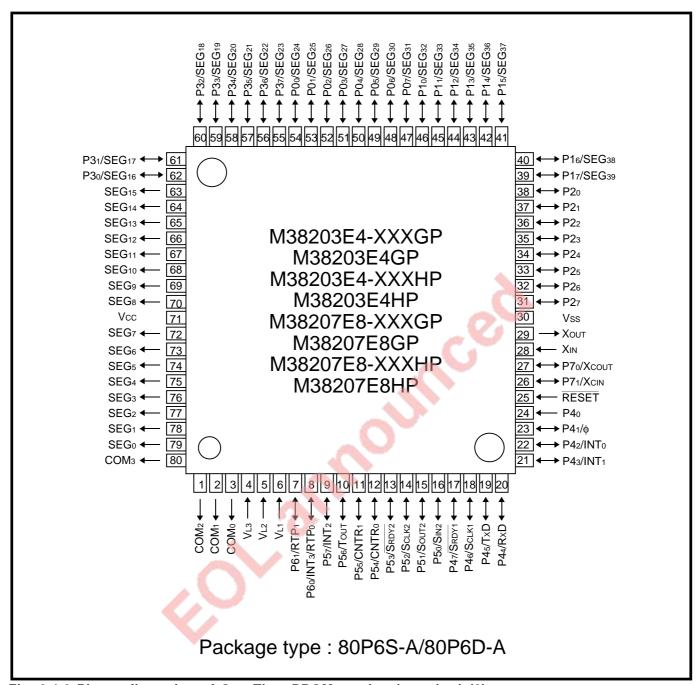

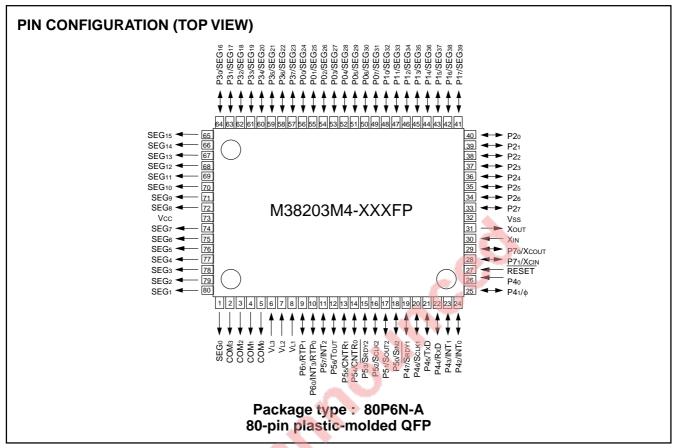

| PIN CONFIGURATION (TOP VIE            | :W)1                              | 1-3 |

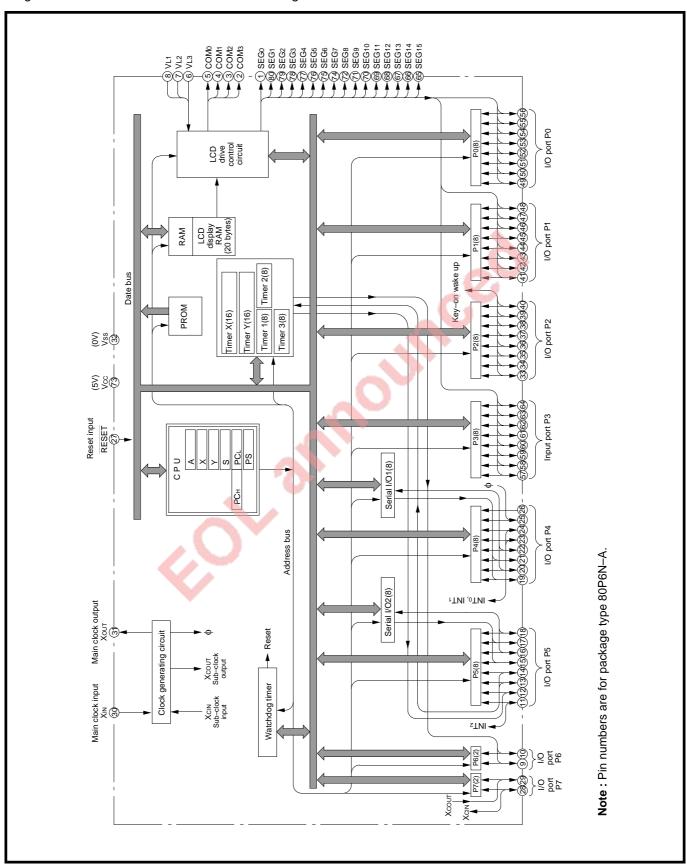

| <b>FUNCTIONAL BLOCK DIAGRAM</b>       | I (Package: 80P6N-A)1             | 1-4 |

| PIN DESCRIPTION                       |                                   | 1-5 |

| PART NUMBERING                        | 1                                 | 1-7 |

|                                       | 1                                 |     |

|                                       | D OPERATING TEMPERATURE VERSION)1 |     |

|                                       | NER SOURCE VOLTAGE VERSION)1-     |     |

| FUNCTIONAL DESCRIPTION                | 1-                                | -11 |

|                                       | 1-                                |     |

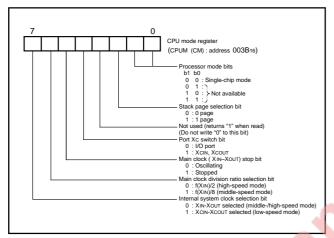

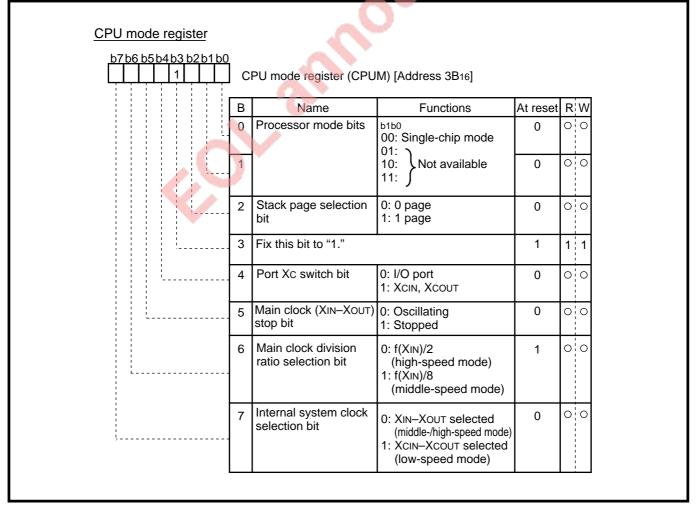

| CPU Mode Register                     | 1-                                | ·11 |

|                                       | 1-                                |     |

|                                       | R) Area1-                         |     |

|                                       | 1-                                |     |

|                                       | 1-                                |     |

|                                       | 1-                                |     |

|                                       | 1-                                |     |

|                                       | 1-                                |     |

|                                       | 1-                                |     |

|                                       | P41–P47, and P5–P7)1-             |     |

| · · · · · · · · · · · · · · · · · · · | nd P1)1-                          |     |

|                                       | 1-                                |     |

|                                       | 1-                                |     |

|                                       | 1-                                |     |

| · · · · · · · · · · · · · · · · · · · | 1-                                |     |

|                                       | 1-                                |     |

|                                       | 1-                                |     |

|                                       | ıke up)1-                         |     |

|                                       | 1-                                |     |

|                                       | 1-                                |     |

|                                       | 1-                                |     |

|                                       | e Edge Selection1-                |     |

|                                       | 1-                                |     |

|                                       | 1-                                |     |

|                                       | e Edge Selection1-                |     |

|                                       | 1-                                |     |

|                                       | 1-                                |     |

|                                       |                                   |     |

|                                       | 1-                                |     |

|                                       | 1-                                |     |

|                                       | Mode1-                            |     |

|                                       | IO1CON) 001A16                    |     |

|                                       | CON) 001B161-                     |     |

|                                       | O1STS) 0019161-                   |     |

|                                       | Register (TB/RB) 0018161-         |     |

|                                       | D1C16                             |     |

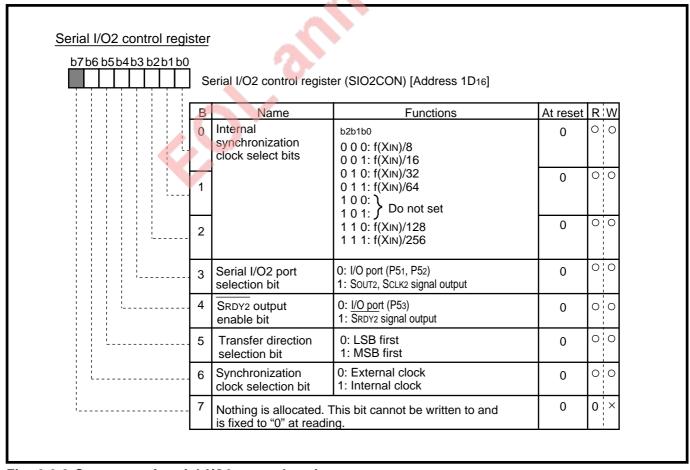

|                                       | IO2CON) 001D161-                  |     |

| Seriai 1/02 Curillui Register (Si     | 020011) 001D16                    | JU  |

| LCD DRIVE CONTROL CIRCUIT                                                 | 1-32 |

|---------------------------------------------------------------------------|------|

| Bias Control and Applied Voltage to LCD Power Input Pins                  | 1-34 |

| Common Pin and Duty Ratio Control                                         | 1-34 |

| LCD Display RAM                                                           | 1-35 |

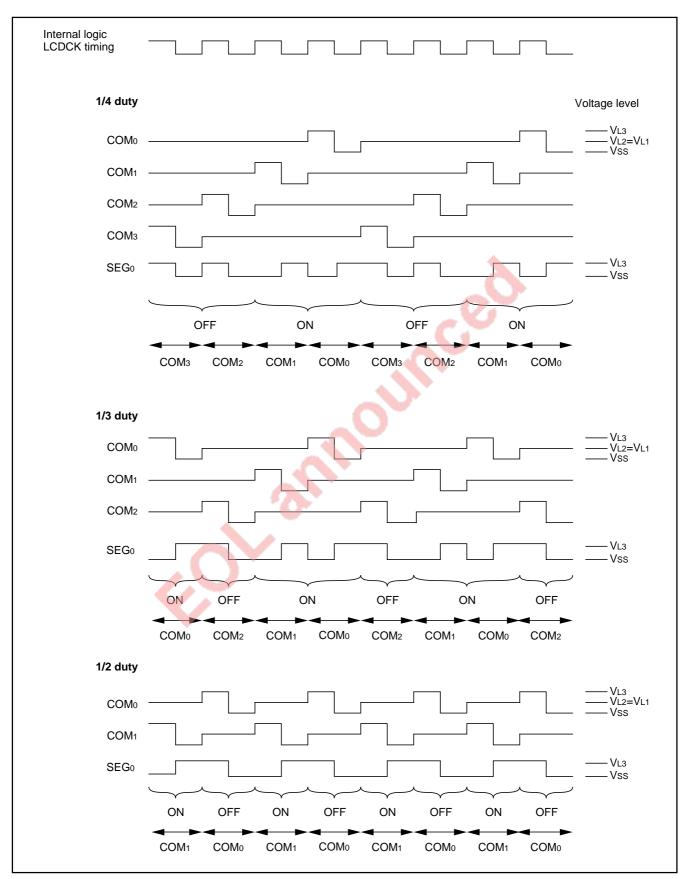

| LCD Drive Timing                                                          | 1-35 |

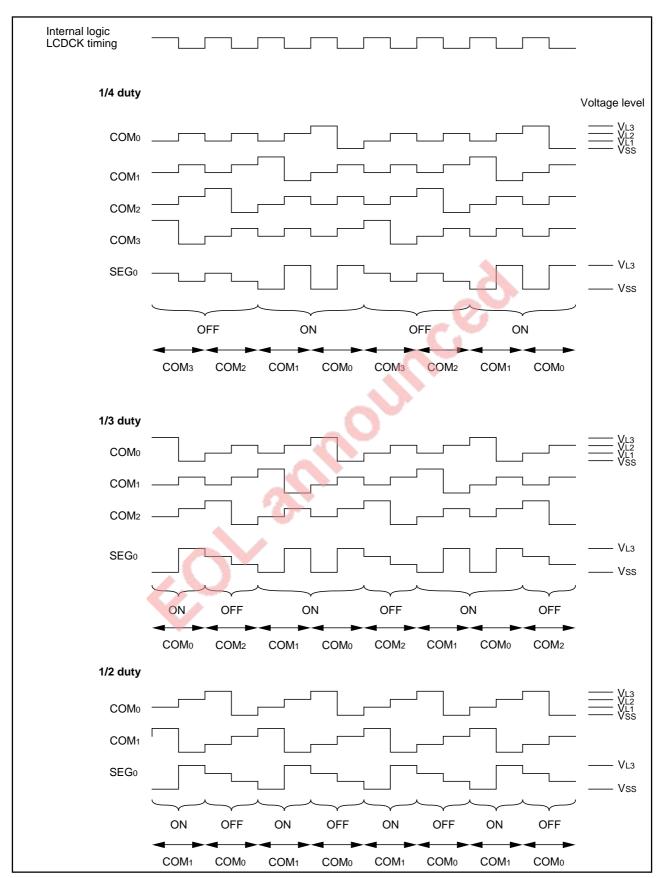

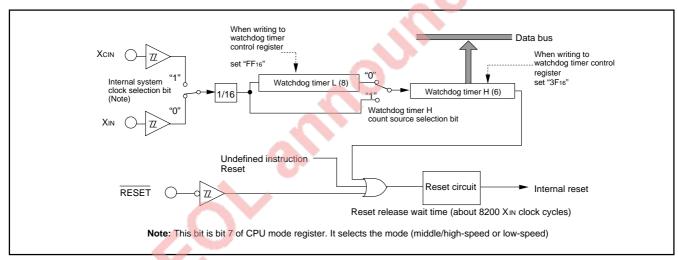

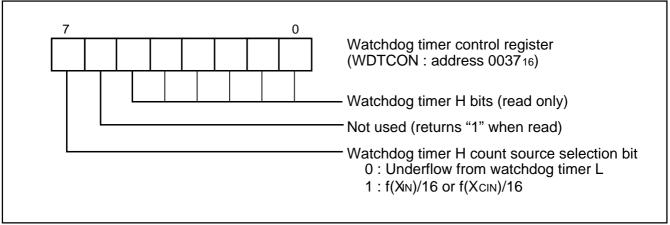

| WATCHDOG TIMER                                                            | 1-38 |

| Initial Value of Watchdog Timer                                           | 1-38 |

| Watchdog Timer Operation                                                  | 1-38 |

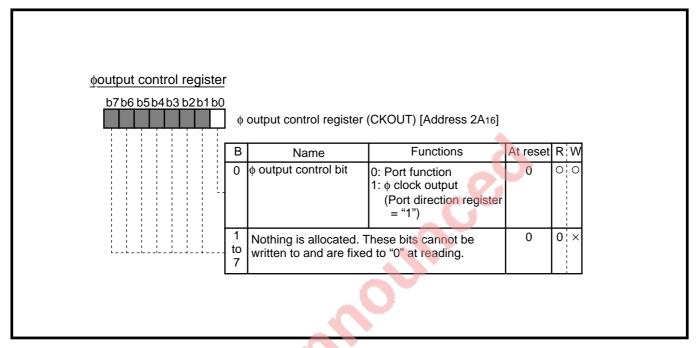

| ♦ CLOCK OUTPUT FUNCTION                                                   |      |

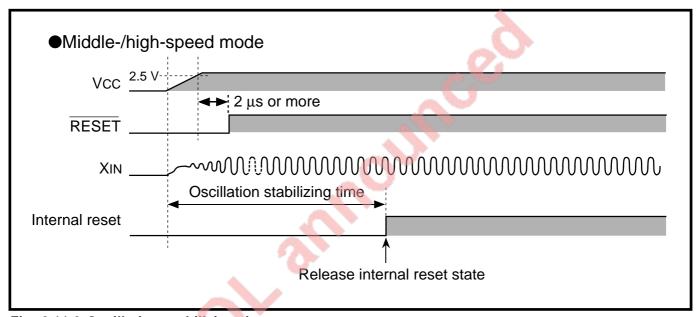

| RESET CIRCUIT                                                             |      |

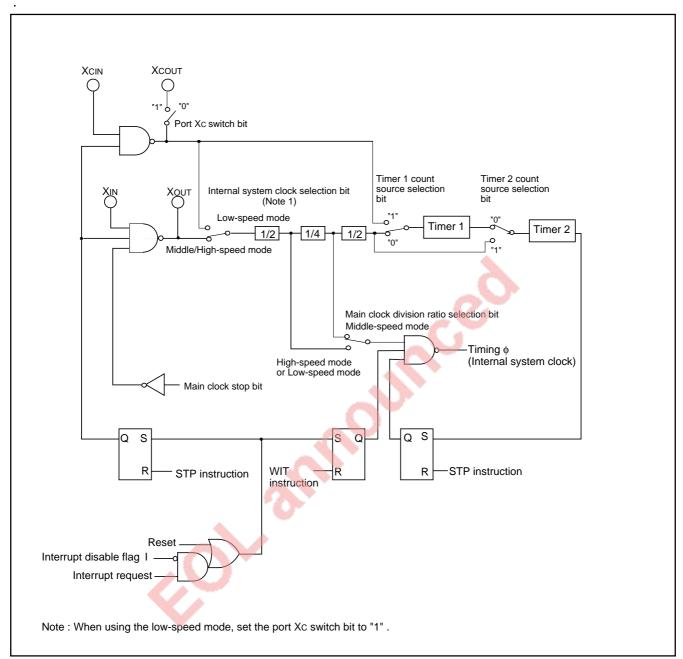

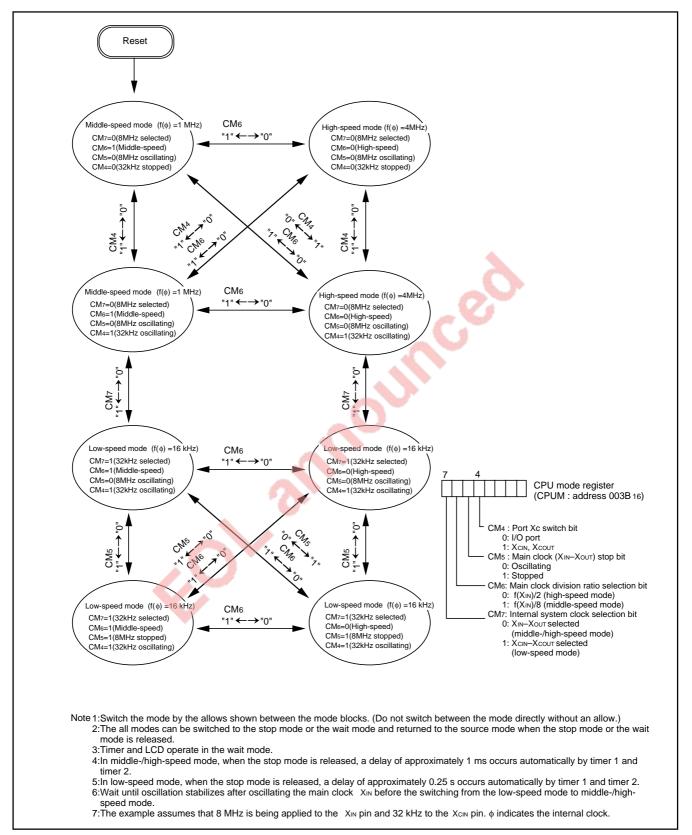

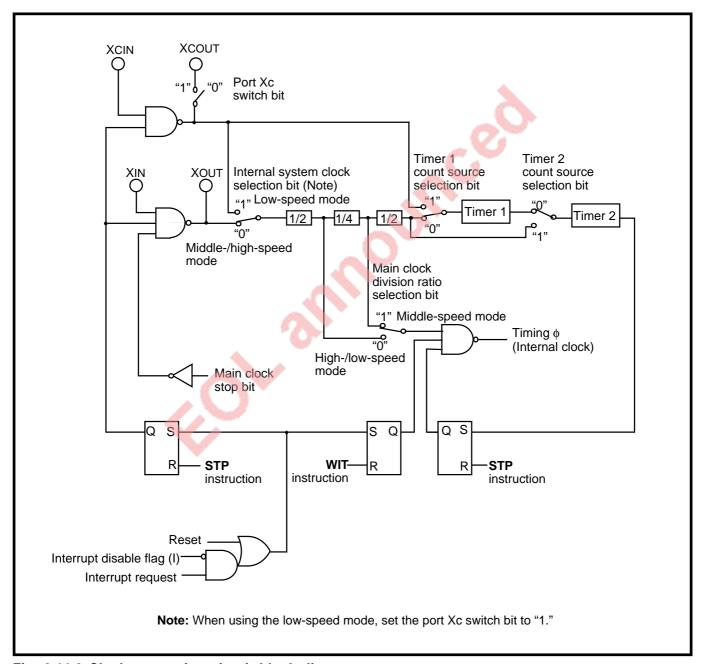

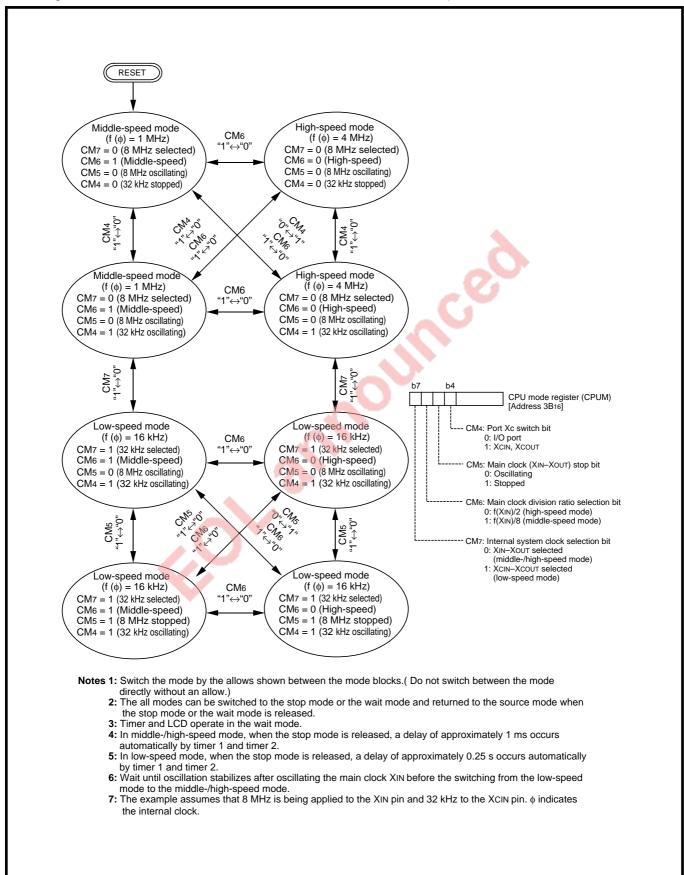

| CLOCK GENERATING CIRCUIT                                                  |      |

| Frequency Control                                                         | 1-42 |

| Oscillation Control                                                       |      |

| NOTES ON PROGRAMMING                                                      |      |

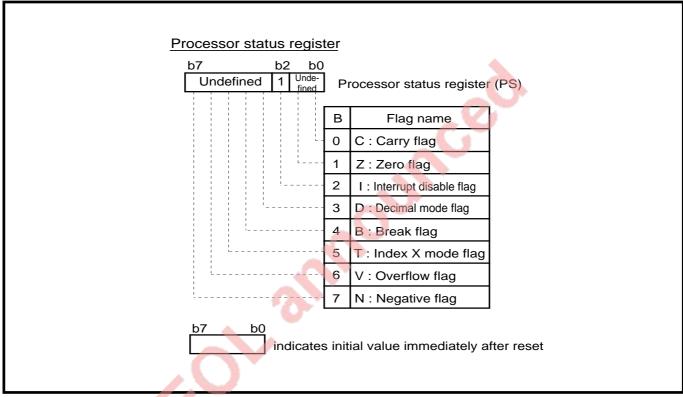

| Processor Status Register                                                 |      |

| Interrupt                                                                 |      |

| Decimal Calculations                                                      |      |

| Timers                                                                    | 1-45 |

| Multiplication and Division Instructions                                  |      |

| Ports                                                                     | _    |

| Serial I/O                                                                |      |

| Instruction Execution Time                                                |      |

| DATA REQUIRED FOR MASK ORDERS                                             |      |

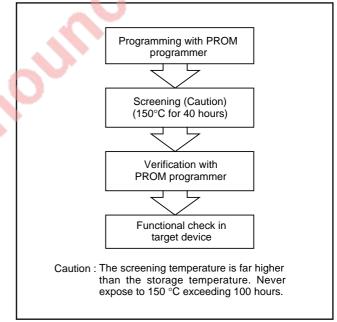

| ROM PROGRAMMIG METHOD                                                     |      |

| Absolute maximum ratings                                                  |      |

| Recommended operating conditions                                          |      |

| Electrical characteristics                                                |      |

| Timing requirements 1                                                     |      |

| Timing requirements 2                                                     |      |

| Switching characteristics 1                                               |      |

| Switching characteristics 2                                               |      |

| Absolute maximum ratings (Extended operating temperature version)         |      |

| Recommended operating conditions (Extended operating temperature version) |      |

| Electrical characteristics (Extended operating temperature version)       |      |

| Timing requirements 1 (Extended operating temperature version)            |      |

| Timing requirements 2 (Extended operating temperature version)            |      |

| Switching characteristics 1 (Extended operating temperature version)      |      |

| Switching characteristics 2 (Extended operating temperature version)      |      |

| Absolute maximum ratings (Low power source voltage version)               |      |

| Recommended operating conditions (Low power source voltage version)       |      |

| Electrical characteristics (Low power source voltage version)             |      |

| Timing requirements 1 (Low power source voltage version)                  |      |

| Timing requirements 2 (Low power source voltage version)                  |      |

| Switching characteristics 1 (Low power source voltage version)            |      |

|                                                                           |      |

| Timing diagramSTANDARD CHARACTERISTICS                                    |      |

|                                                                           |      |

| Power Source Current Characteristic Examples (Icc-Vcc characteristics)    |      |

| Port Standard Characteristic Examples                                     |      |

|                                                                           |      |

### **CHAPTER 2. APPLICATION**

| 2.4         | I/O pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2 2                                                                                    |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| <b>2.</b> I | 2.1.1 I/O ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                        |

|             | 2.1.2 Function pins                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                        |

|             | 2.1.2 Puriction pins                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                        |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                        |

|             | 2.1.4 Notes on use                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                        |

| 2.2         | Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                        |

|             | 2.2.1 Explanation of operations                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                        |

|             | 2.2.2 Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                        |

|             | 2.2.3 Related registers                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                        |

|             | 2.2.4 INT interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                        |

|             | 2.2.5 Key input interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                        |

|             | 2.2.6 Notes on use                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                        |

| 2.3         | Timer X and timer Y                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                        |

|             | 2.3.1 Explanation of timer X operations                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                        |

|             | 2.3.2 Explanation of timer Y operations                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                        |

|             | 2.3.3 Related registers                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                        |

|             | 2.3.4 Register setting example                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                        |

|             | 2.3.5 Application examples                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                        |

|             | 2.3.6 Notes on use                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                        |

| 2.4         | Timer 1, timer 2, and timer 3                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-85                                                                                   |

|             | 2.4.1 Explanation of operations                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-85                                                                                   |

|             | 2.4.2 Related registers                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-90                                                                                   |

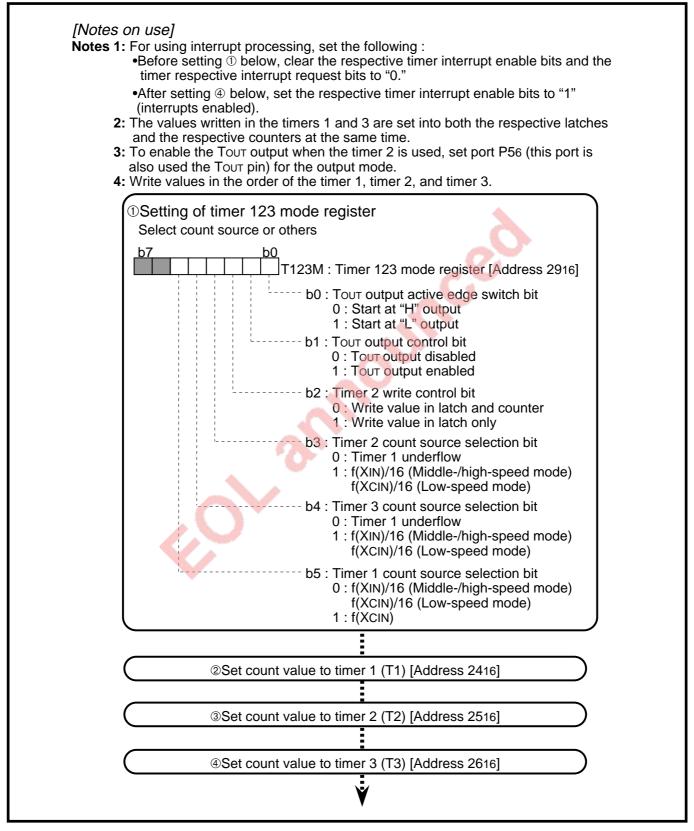

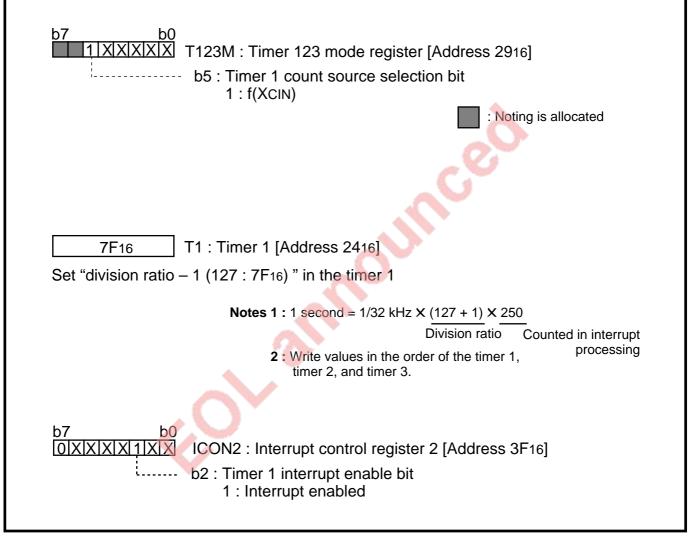

|             | 2.4.3 Register setting example                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-99                                                                                   |

|             | 2.4.4 Application example                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-100                                                                                  |

|             | 2.4.5 Notes on use                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-102                                                                                  |

| 2 E         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0.400                                                                                  |

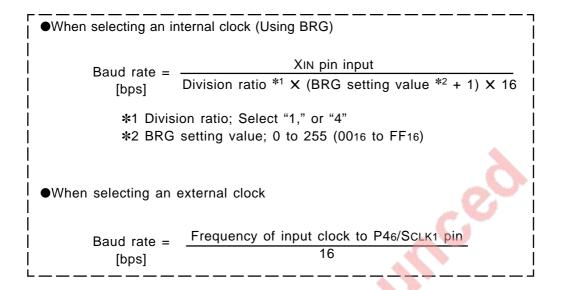

| 2.5         | Serial I/O1                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Z-103                                                                                  |

| 2.5         | 2.5.1 Explanation of operations                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-103                                                                                  |

| 2.5         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-103                                                                                  |

| 2.3         | 2.5.1 Explanation of operations                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-103<br>2-120<br>2-121                                                                |

| 2.5         | 2.5.1 Explanation of operations                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-103<br>2-120<br>2-121                                                                |

| 2.5         | 2.5.1 Explanation of operations                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-103<br>2-120<br>2-121                                                                |

|             | 2.5.1 Explanation of operations 2.5.2 Pins 2.5.3 Related registers 2.5.4 Register setting example                                                                                                                                                                                                                                                                                                                                                                                 | 2-103<br>2-120<br>2-121<br>2-129                                                       |

|             | 2.5.1 Explanation of operations 2.5.2 Pins 2.5.3 Related registers 2.5.4 Register setting example 2.5.5 Notes on use                                                                                                                                                                                                                                                                                                                                                              | 2-103<br>2-120<br>2-121<br>2-129<br>2-139                                              |

|             | 2.5.1 Explanation of operations 2.5.2 Pins 2.5.3 Related registers 2.5.4 Register setting example 2.5.5 Notes on use Serial I/O2                                                                                                                                                                                                                                                                                                                                                  | 2-103<br>2-120<br>2-121<br>2-139<br>2-141                                              |

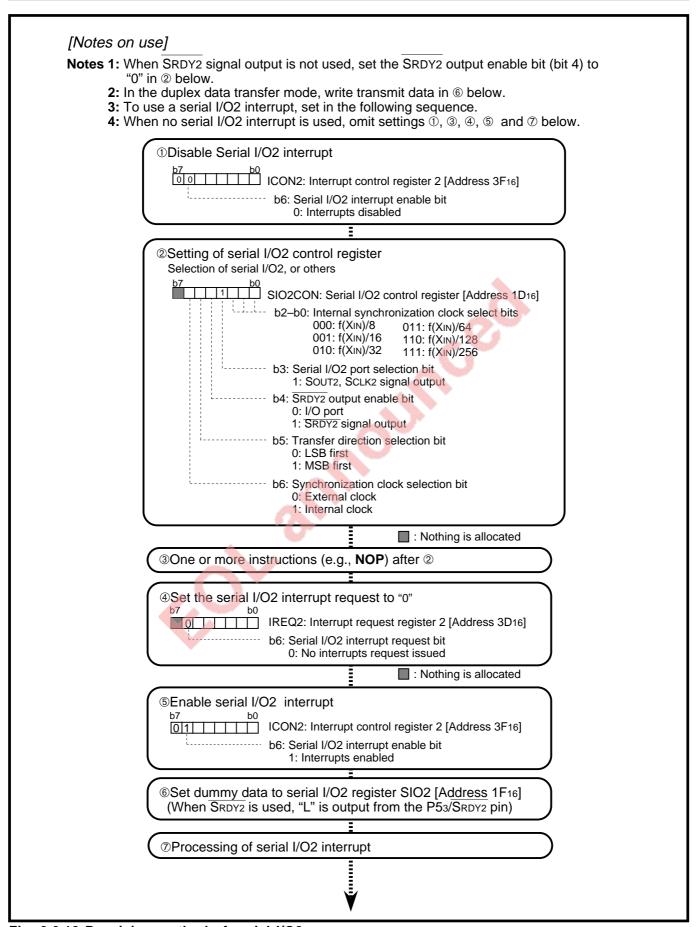

|             | 2.5.1 Explanation of operations 2.5.2 Pins 2.5.3 Related registers 2.5.4 Register setting example 2.5.5 Notes on use 3 Serial I/O2 2.6.1 Explanation of operations                                                                                                                                                                                                                                                                                                                | 2-1032-1202-1212-1392-1412-144                                                         |

|             | 2.5.1 Explanation of operations 2.5.2 Pins 2.5.3 Related registers 2.5.4 Register setting example 2.5.5 Notes on use Serial I/O2 2.6.1 Explanation of operations 2.6.2 Pins                                                                                                                                                                                                                                                                                                       | 2-103<br>2-120<br>2-121<br>2-139<br>2-141<br>2-148<br>2-149                            |

| 2.6         | 2.5.1 Explanation of operations 2.5.2 Pins 2.5.3 Related registers 2.5.4 Register setting example 2.5.5 Notes on use Serial I/O2 2.6.1 Explanation of operations 2.6.2 Pins 2.6.3 Related registers 2.6.4 Register setting example 2.6.5 Notes on use                                                                                                                                                                                                                             | 2-103<br>2-120<br>2-129<br>2-139<br>2-141<br>2-148<br>2-149<br>2-152                   |

| 2.6         | 2.5.1 Explanation of operations 2.5.2 Pins 2.5.3 Related registers 2.5.4 Register setting example 2.5.5 Notes on use Serial I/O2 2.6.1 Explanation of operations 2.6.2 Pins 2.6.3 Related registers 2.6.4 Register setting example                                                                                                                                                                                                                                                | 2-103<br>2-120<br>2-129<br>2-139<br>2-141<br>2-148<br>2-149<br>2-152                   |

| 2.6         | 2.5.1 Explanation of operations 2.5.2 Pins 2.5.3 Related registers 2.5.4 Register setting example 2.5.5 Notes on use Serial I/O2 2.6.1 Explanation of operations 2.6.2 Pins 2.6.3 Related registers 2.6.4 Register setting example 2.6.5 Notes on use                                                                                                                                                                                                                             | 2-1032-1202-1292-1392-1412-1442-1452-155                                               |

| 2.6         | 2.5.1 Explanation of operations 2.5.2 Pins 2.5.3 Related registers 2.5.4 Register setting example 2.5.5 Notes on use  Serial I/O2 2.6.1 Explanation of operations 2.6.2 Pins 2.6.3 Related registers 2.6.4 Register setting example 2.6.5 Notes on use  LCD drive control circuit                                                                                                                                                                                                 | 2-1032-1202-1292-1392-1412-1482-1522-154                                               |

| 2.6         | 2.5.1 Explanation of operations 2.5.2 Pins 2.5.3 Related registers 2.5.4 Register setting example 2.5.5 Notes on use  Serial I/O2 2.6.1 Explanation of operations 2.6.2 Pins 2.6.3 Related registers 2.6.4 Register setting example 2.6.5 Notes on use  LCD drive control circuit 2.7.1 Explanation of operations                                                                                                                                                                 | 2-1032-1202-1212-1392-1412-1482-1522-155                                               |

| 2.6         | 2.5.1 Explanation of operations 2.5.2 Pins 2.5.3 Related registers 2.5.4 Register setting example 2.5.5 Notes on use  Serial I/O2 2.6.1 Explanation of operations 2.6.2 Pins 2.6.3 Related registers 2.6.4 Register setting example 2.6.5 Notes on use  CLCD drive control circuit 2.7.1 Explanation of operations 2.7.2 Pins                                                                                                                                                     | 2-103<br>2-120<br>2-121<br>2-139<br>2-141<br>2-148<br>2-152<br>2-155<br>2-155          |

| 2.6         | 2.5.1 Explanation of operations 2.5.2 Pins                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-103<br>2-120<br>2-129<br>2-139<br>2-141<br>2-148<br>2-152<br>2-155<br>2-155<br>2-156 |

| 2.6         | 2.5.1 Explanation of operations 2.5.2 Pins                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-1032-1202-1212-1392-1412-1482-1522-1552-1562-166                                     |

| 2.6         | 2.5.1 Explanation of operations 2.5.2 Pins 2.5.3 Related registers 2.5.4 Register setting example 2.5.5 Notes on use  Serial I/O2 2.6.1 Explanation of operations 2.6.2 Pins 2.6.3 Related registers 2.6.4 Register setting example 2.6.5 Notes on use  CLD drive control circuit 2.7.1 Explanation of operations 2.7.2 Pins 2.7.3 Related registers 2.7.4 Register setting example 2.7.5 Application examples 2.7.5 Application examples 2.7.6 Notes on use                      | 2-1032-1202-1212-1392-1412-1482-1522-1552-1562-1662-168                                |

| 2.6         | 2.5.1 Explanation of operations 2.5.2 Pins 2.5.3 Related registers 2.5.4 Register setting example 2.5.5 Notes on use  Serial I/O2 2.6.1 Explanation of operations 2.6.2 Pins 2.6.3 Related registers 2.6.4 Register setting example 2.6.5 Notes on use  LCD drive control circuit 2.7.1 Explanation of operations 2.7.2 Pins 2.7.3 Related registers 2.7.4 Register setting example 2.7.5 Application examples 2.7.6 Notes on use  Watchdog timer                                 | 2-1032-1202-1212-1392-1412-1482-1482-1562-1562-1562-1662-173                           |

| 2.6         | 2.5.1 Explanation of operations 2.5.2 Pins 2.5.3 Related registers 2.5.4 Register setting example 2.5.5 Notes on use  Serial I/O2 2.6.1 Explanation of operations 2.6.2 Pins 2.6.3 Related registers 2.6.4 Register setting example 2.6.5 Notes on use  LCD drive control circuit 2.7.1 Explanation of operations 2.7.2 Pins 2.7.3 Related registers 2.7.4 Register setting example 2.7.5 Application examples 2.7.6 Notes on use  Watchdog timer 2.8.1 Explanation of operations | 2-1032-1202-1212-1392-1412-1482-1552-1552-1562-1662-1682-1732-173                      |

| 2.6         | 2.5.1 Explanation of operations 2.5.2 Pins 2.5.3 Related registers 2.5.4 Register setting example 2.5.5 Notes on use  Serial I/O2 2.6.1 Explanation of operations 2.6.2 Pins 2.6.3 Related registers 2.6.4 Register setting example 2.6.5 Notes on use  LCD drive control circuit 2.7.1 Explanation of operations 2.7.2 Pins 2.7.3 Related registers 2.7.4 Register setting example 2.7.5 Application examples 2.7.6 Notes on use  Watchdog timer                                 | 2-1032-1202-1292-1392-1412-1482-1552-1552-1562-1662-1732-173                           |

| 2.6         | 2.5.1 Explanation of operations 2.5.2 Pins                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-1032-1202-1292-1392-1412-1482-1552-1562-1562-1682-1732-173                           |

| 2.6         | 2.5.1 Explanation of operations 2.5.2 Pins                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-1032-1202-1212-1392-1412-1482-1482-1552-1562-1562-1762-1762-1772-176                 |

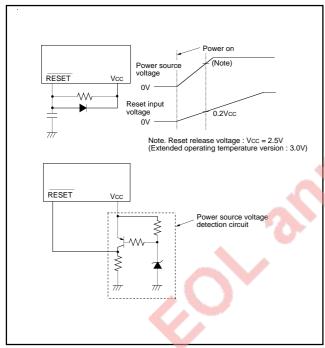

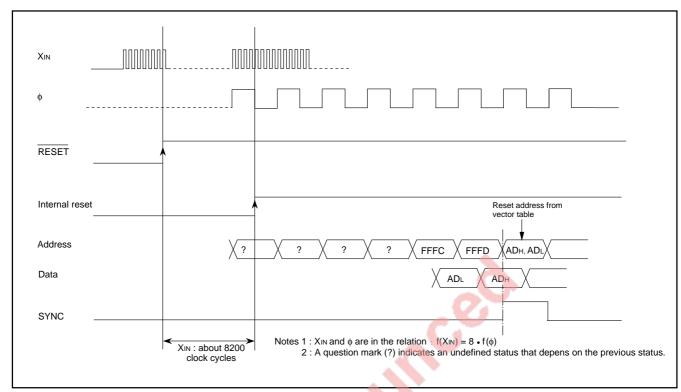

|         | 2.10 Reset                                                                                     | 2-185 |

|---------|------------------------------------------------------------------------------------------------|-------|

|         | 2.10.1 Explanation of operations                                                               |       |

|         | 2.10.2 Internal state of the microcomputer immediately after reset release                     | 2-187 |

|         | 2.10.3 Reset circuit                                                                           |       |

|         | 2.10.4 Notes on the RESET pin                                                                  |       |

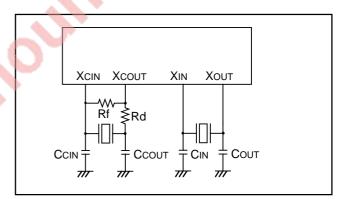

|         | 2.11 Oscillation circuit                                                                       | 2-190 |

|         | 2.11.1 Oscillation circuit                                                                     |       |

|         | 2.11.2 Internal clock φ                                                                        | 2-192 |

|         | 2.11.3 Oscillating operation                                                                   | 2-194 |

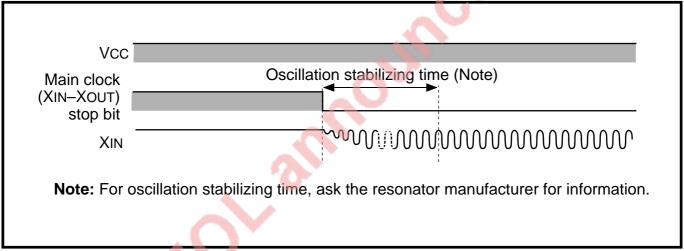

|         | 2.11.4 Oscillation stabilizing time                                                            | 2-197 |

| CHAPTER | 3. APPENDIX                                                                                    |       |

|         | 3.1 Built-in PROM version                                                                      | 3-2   |

|         | 3.1.1 Product expansion                                                                        |       |

|         | 3.1.2 Performance overview                                                                     |       |

|         | 3.1.3 Pin configuration                                                                        |       |

|         | 3.1.4 Functional block diagram                                                                 |       |

|         | 3.1.5 Notes on use                                                                             | 3-9   |

|         | 3.2 Countermeasures against noise                                                              | 3-11  |

|         | 3.2.1 Shortest wiring length                                                                   | 3-11  |

|         | 3.2.2 Connection of a bypass capacitor across the Vss line and the Vcc line                    | 3-12  |

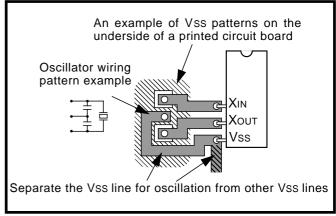

|         | 3.2.3 Oscillator concerns                                                                      | 3-13  |

|         | 3.2.4 Installing an oscillator away from signal lines where potential levels change frequently | 3-14  |

|         | 3.2.5 Oscillator protection using Vss pattern                                                  | 3-14  |

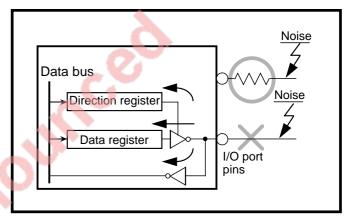

|         | 3.2.6 Set up for I/O ports                                                                     | 3-14  |

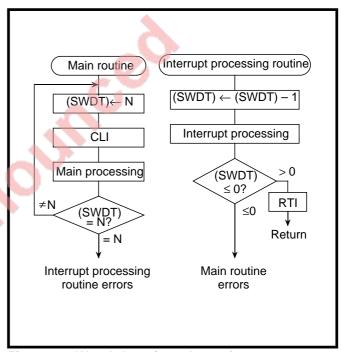

|         | 3.2.7 Providing of watchdog timer function by software                                         | 3-15  |

|         | 3.3 Control registers                                                                          |       |

|         | 3.4 List of instruction codes                                                                  | 3-29  |

|         | 3.5 Machine instructions                                                                       |       |

|         | 3.6 Mask ROM ordering method                                                                   |       |

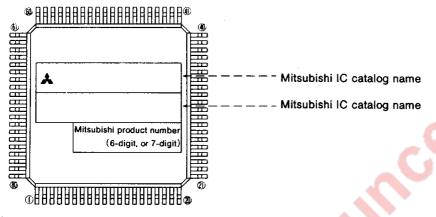

|         | 3.7 Mark specification form                                                                    |       |

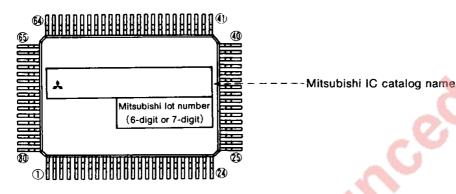

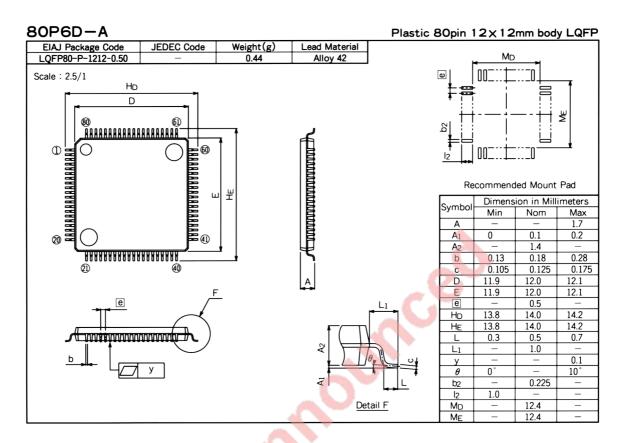

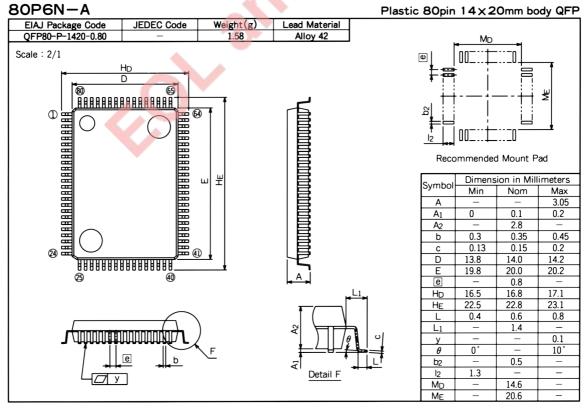

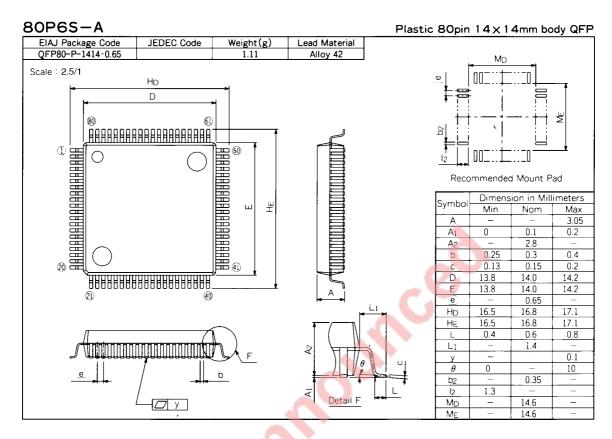

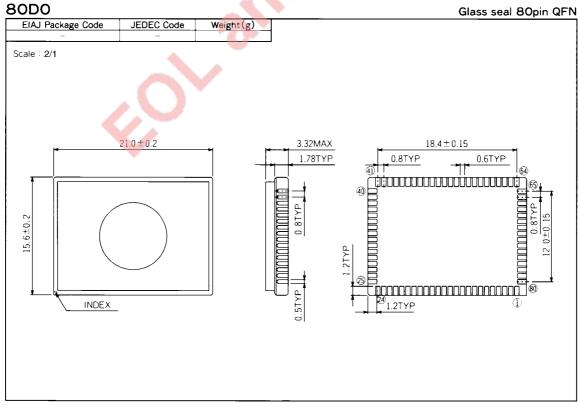

|         | 3.8 Package outlines                                                                           |       |

|         | 3.9 SFR allocation                                                                             |       |

|         | 3.10 Pin configuration                                                                         | 3-57  |

# **List of figures**

### **CHAPTER 1. HARDWARE**

| Fig. | 1 Pin configuration of M38203M4-XXXFP                                          | .1-2                     |

|------|--------------------------------------------------------------------------------|--------------------------|

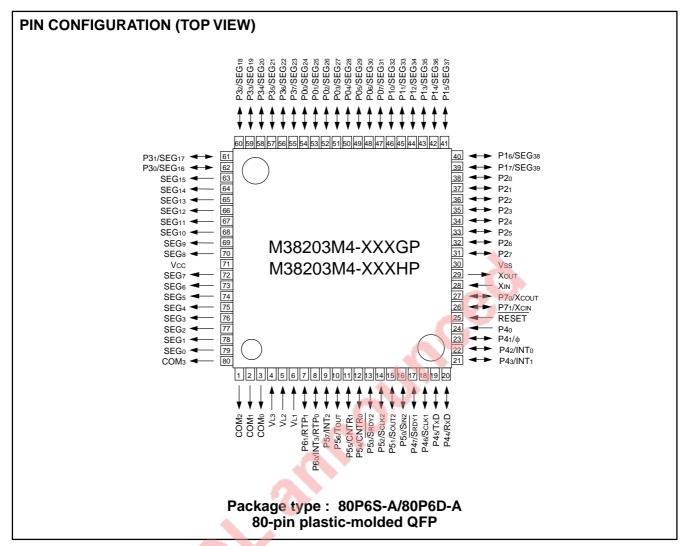

| Fig. | 2 Pin configuration of M38203M4-XXXGP/HP                                       | . 1-3                    |

|      | 3 Function block diagram                                                       |                          |

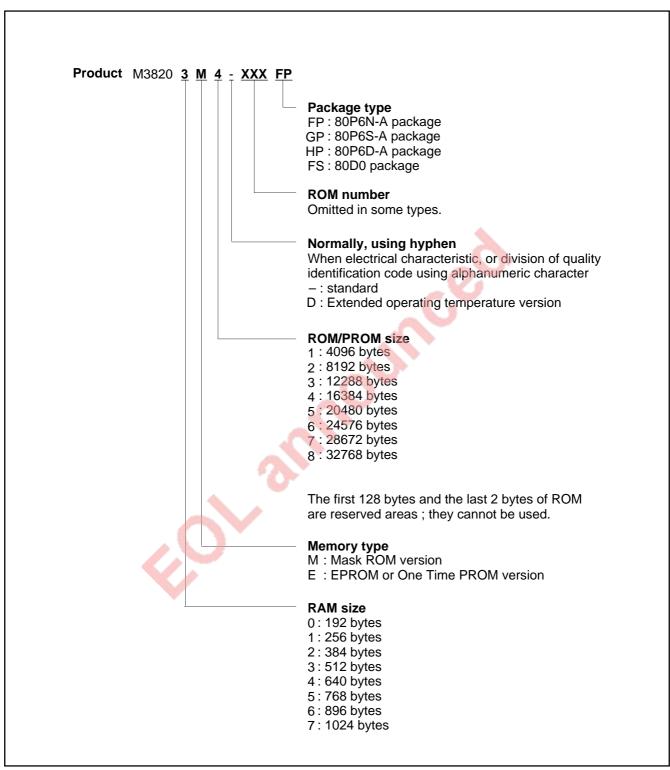

|      | 4 Part numbering                                                               |                          |

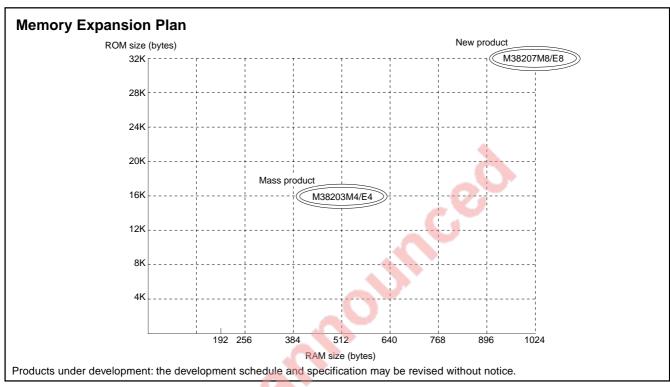

|      | 5 Memory expansion plan (1)                                                    |                          |

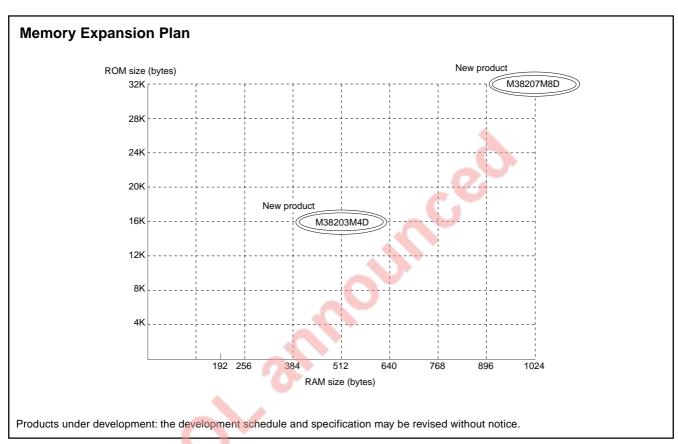

|      | 6 Memory expansion plan (2)                                                    |                          |

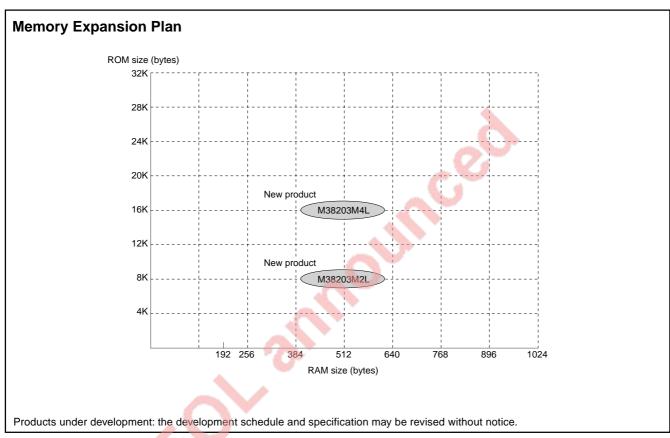

|      | 7 Memory expansion plan (3)                                                    |                          |

|      | 8 Structure of CPU mode register                                               |                          |

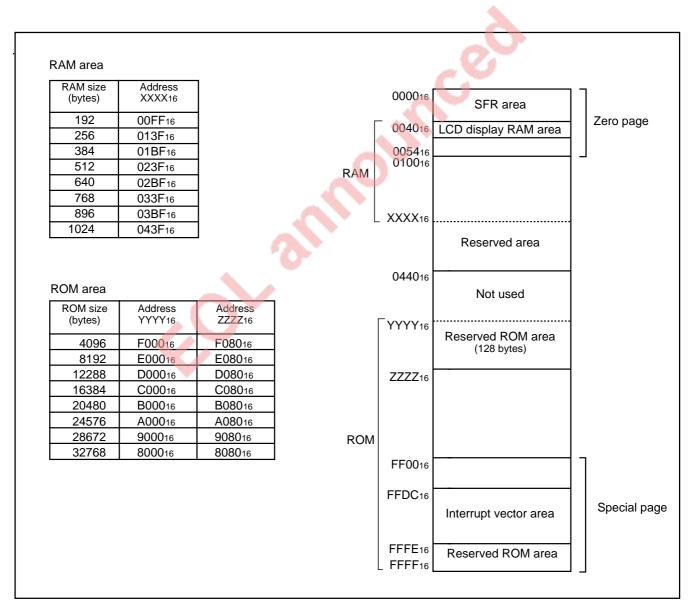

|      | 9 Memory map diagram                                                           |                          |

|      | 10 Memory map of special function register (SFR)                               |                          |

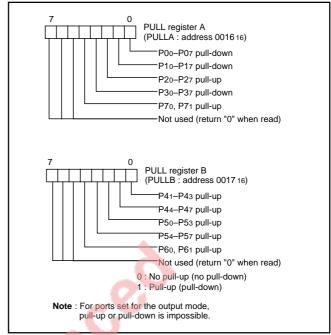

|      | 11 Structure of PULL register A and PULL register B                            |                          |

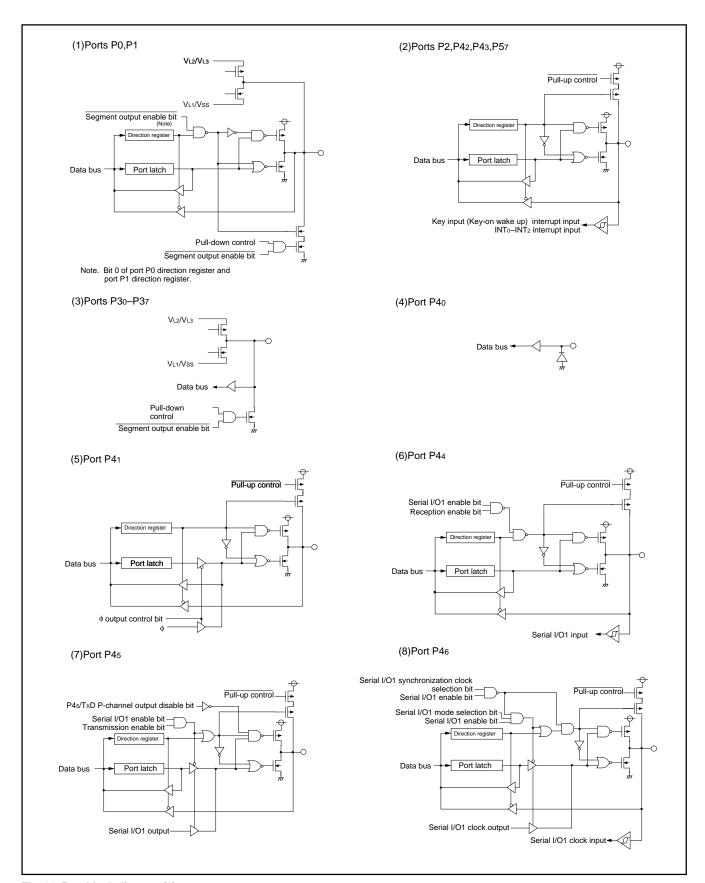

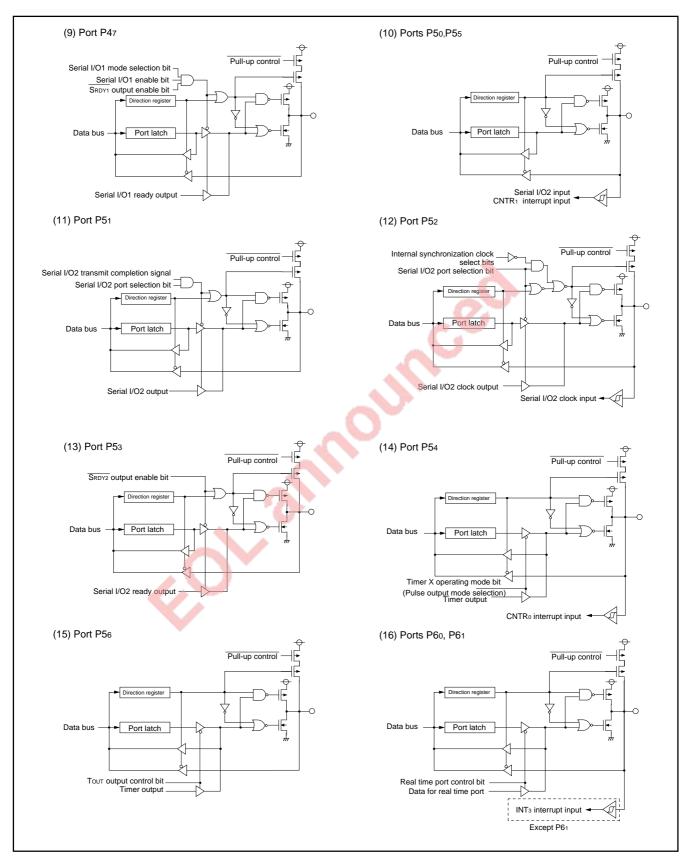

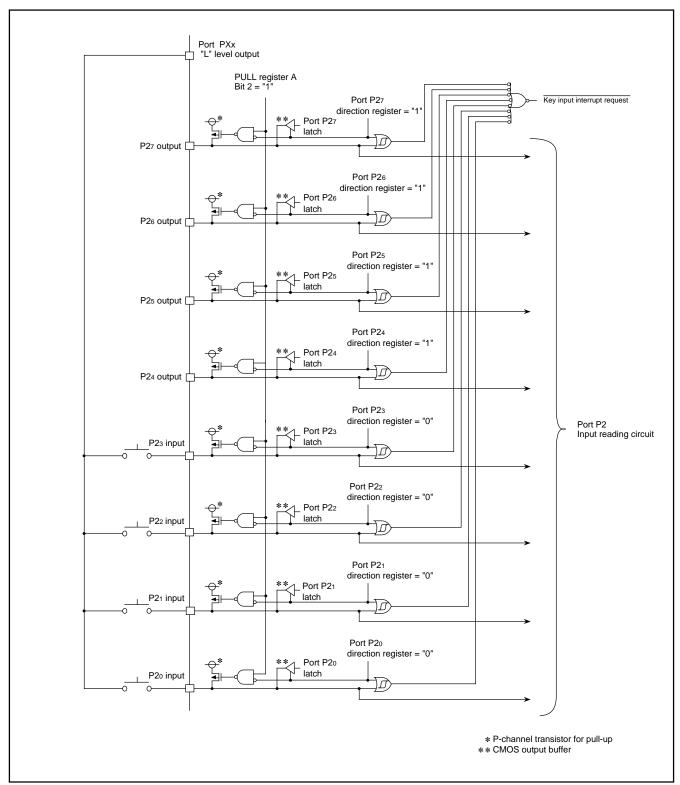

|      | 12 Port block diagram (1)                                                      |                          |

|      | 13 Port block diagram (2)                                                      |                          |

|      | 14 Port block diagram (3)                                                      |                          |

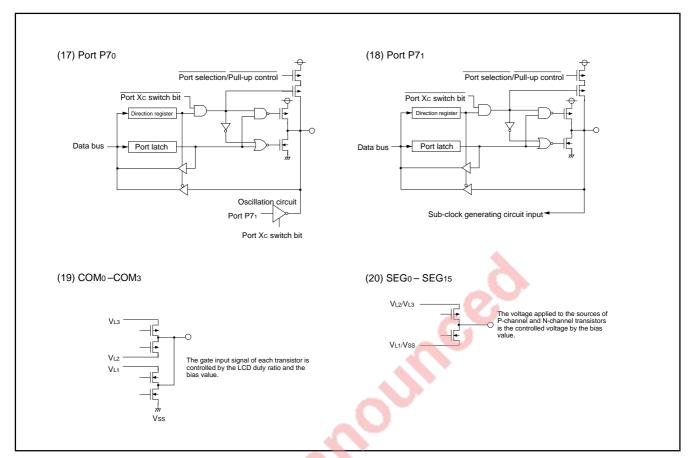

|      | 15 Interrupt control                                                           |                          |

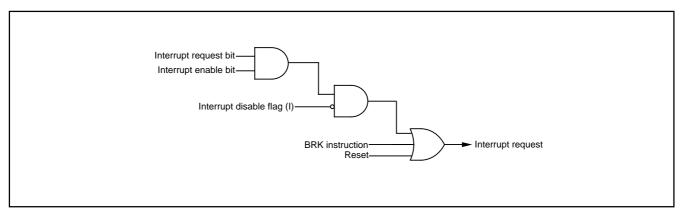

|      | 16 Structure of interrupt-related registers                                    |                          |

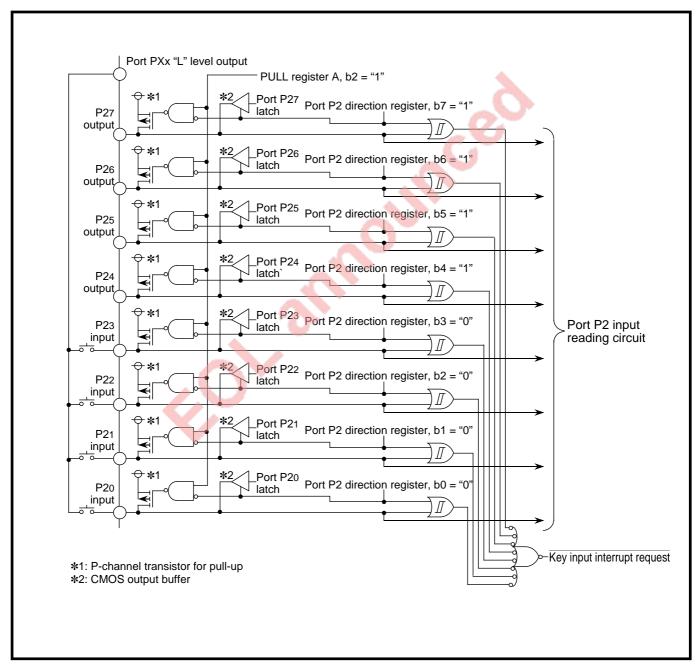

|      | 17 Connection example when using key input interrupt and port P2 block diagram |                          |

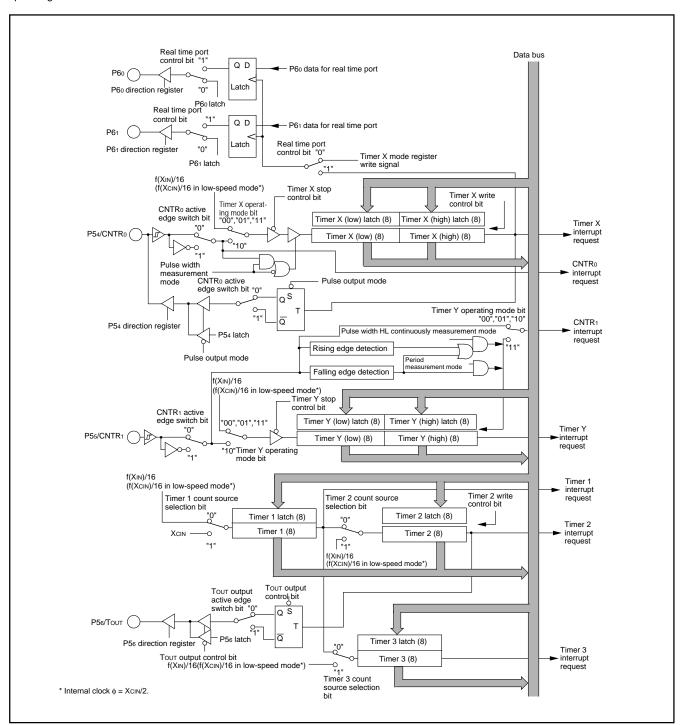

|      | 18 Timer block diagram                                                         |                          |

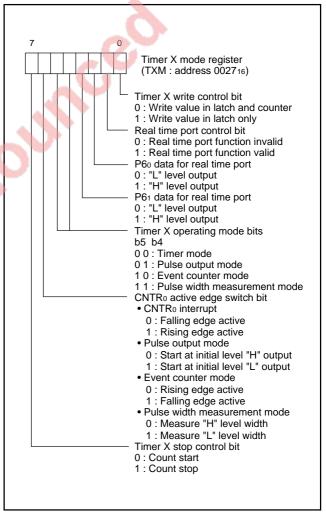

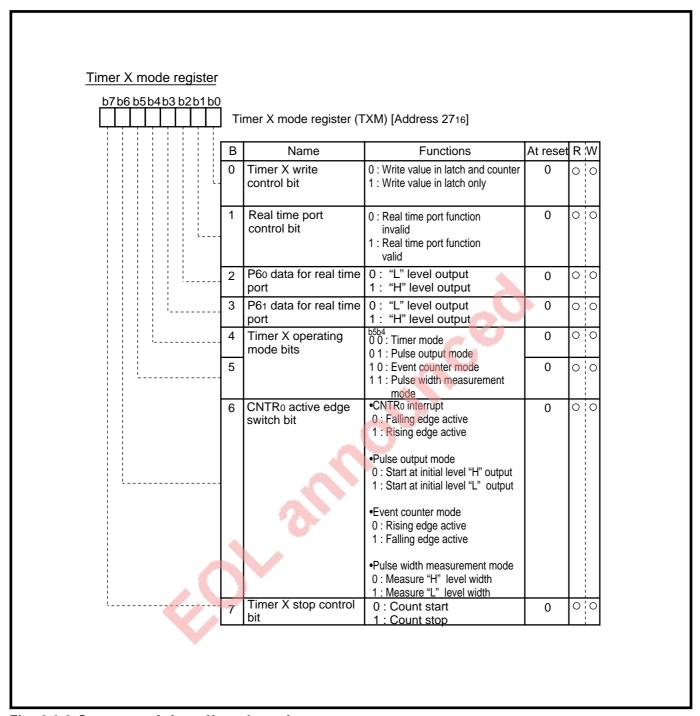

| _    | 19 Structure of timer X mode register                                          |                          |

|      |                                                                                |                          |

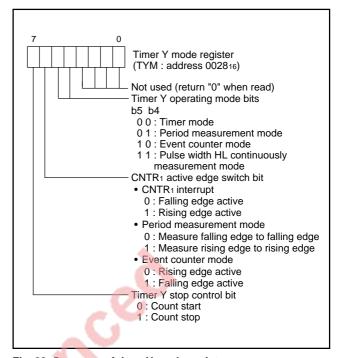

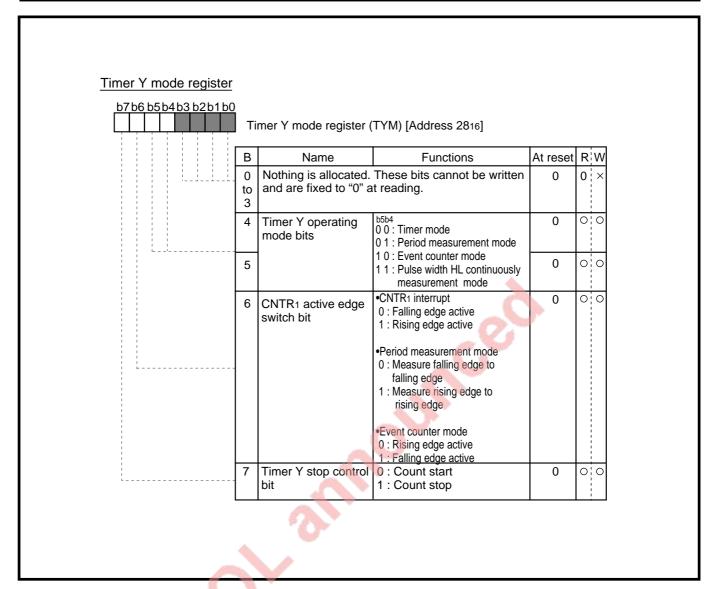

| Fig. | 20 Structure of timer Y mode register                                          | 1-2 <del>-</del><br>1-25 |

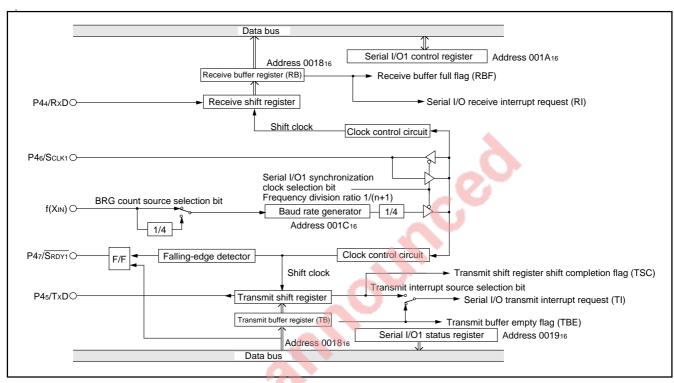

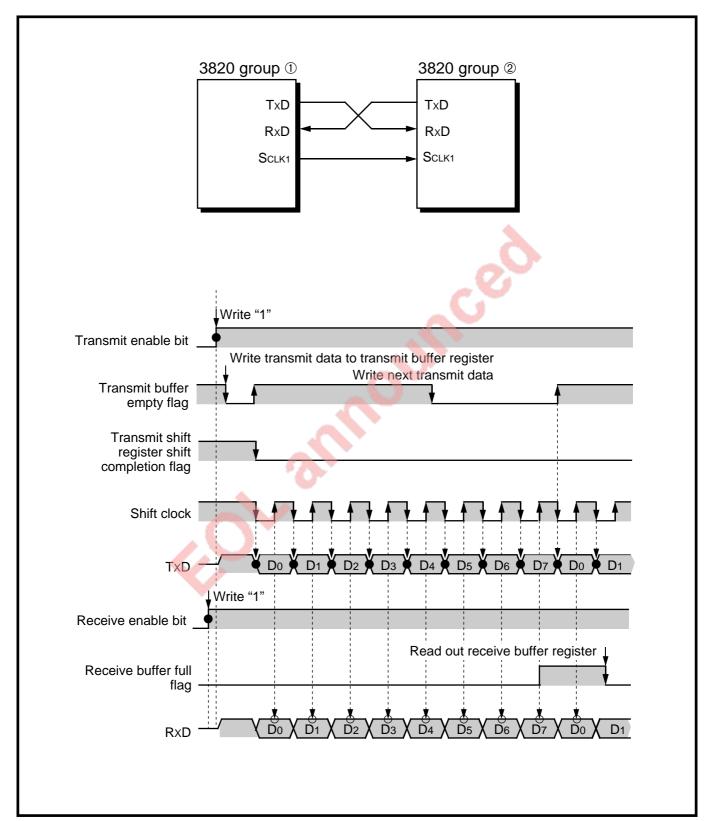

|      | 22 Block diagram of clock synchronous serial I/O1                              |                          |

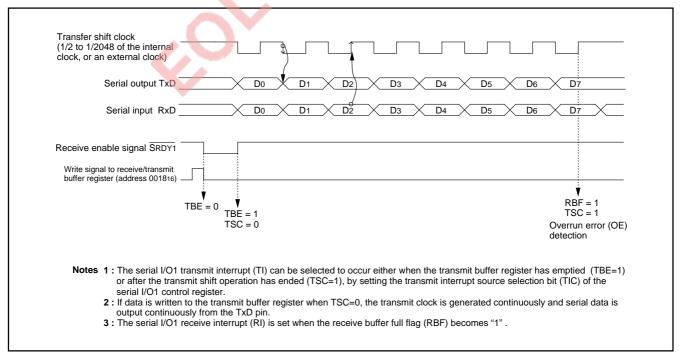

|      | 23 Operation of clock synchronous serial I/O1 function                         |                          |

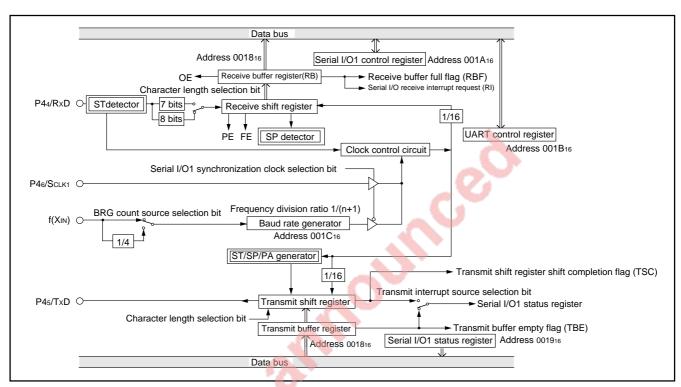

|      | 24 Block diagram of UART serial I/O1                                           |                          |

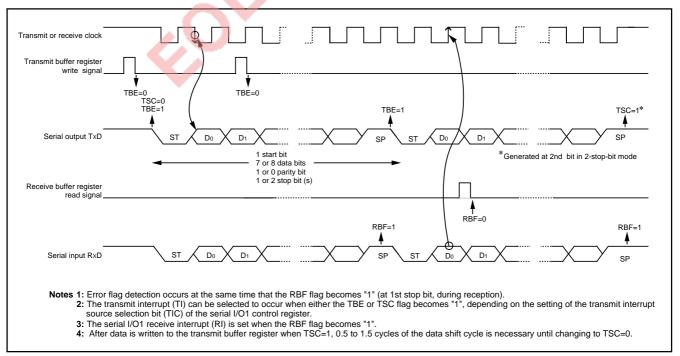

|      | 25 Operation of UART serial I/O1 function                                      |                          |

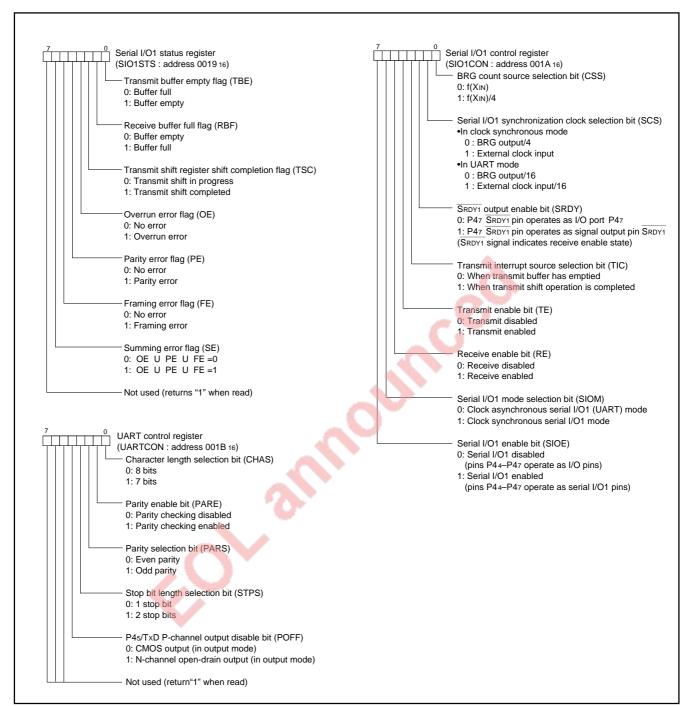

|      | 26 Structure of serial I/O1 control registers                                  |                          |

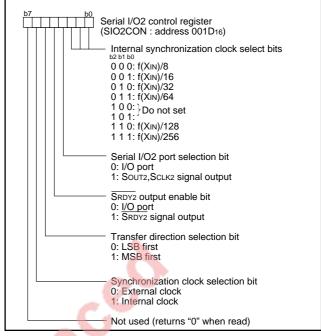

|      | 27 Structure of serial I/O2 control register                                   |                          |

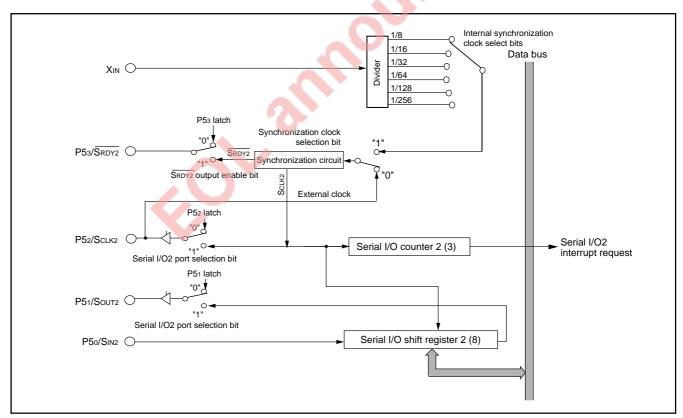

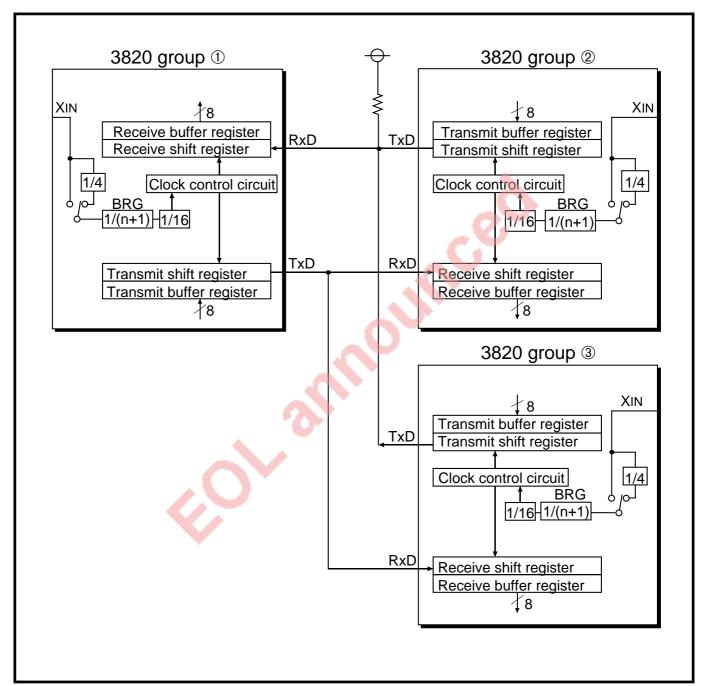

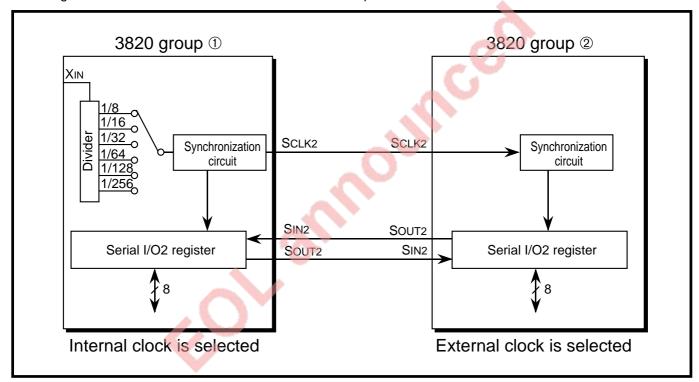

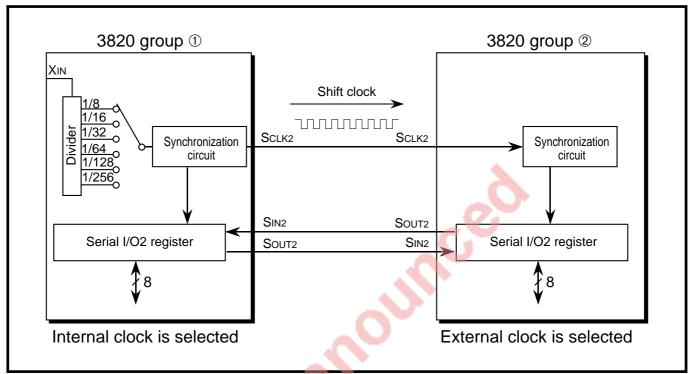

|      | 28 Block diagram of serial I/O2 function                                       |                          |

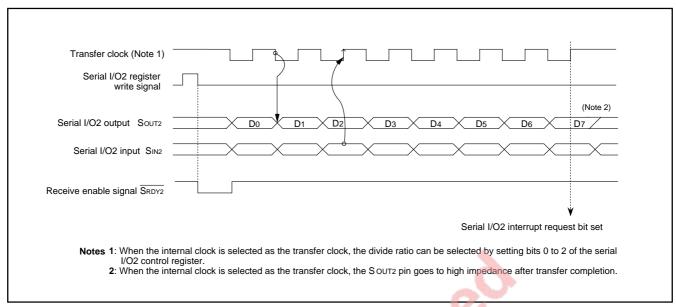

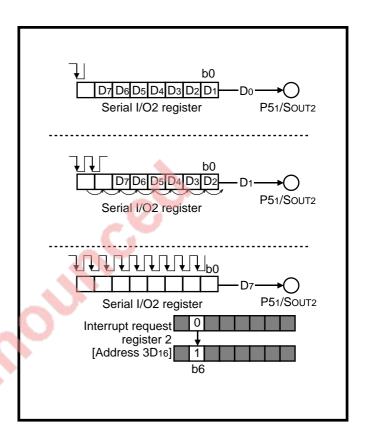

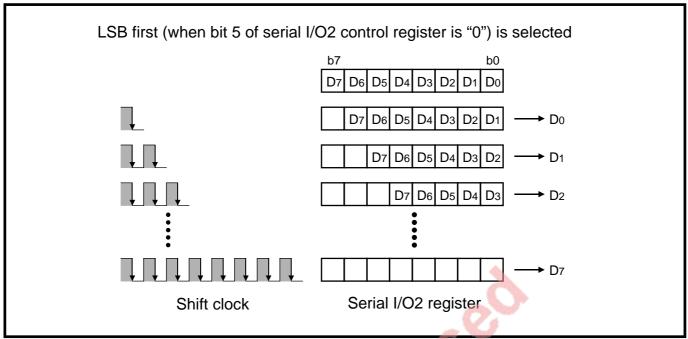

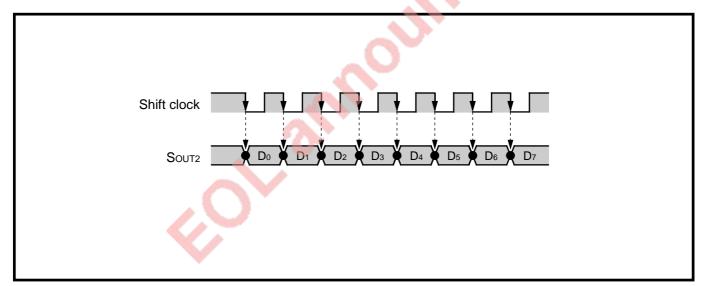

| rig. | 29 Timing of serial I/O2 function                                              | 1-30                     |

|      |                                                                                |                          |

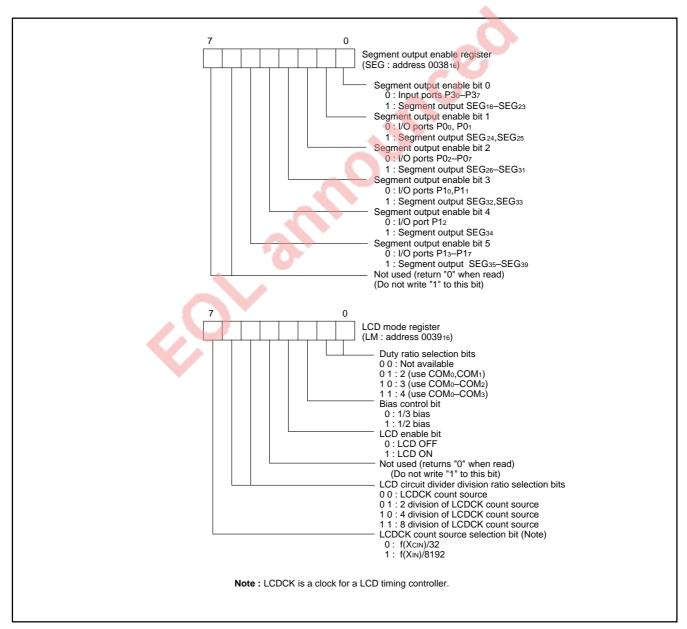

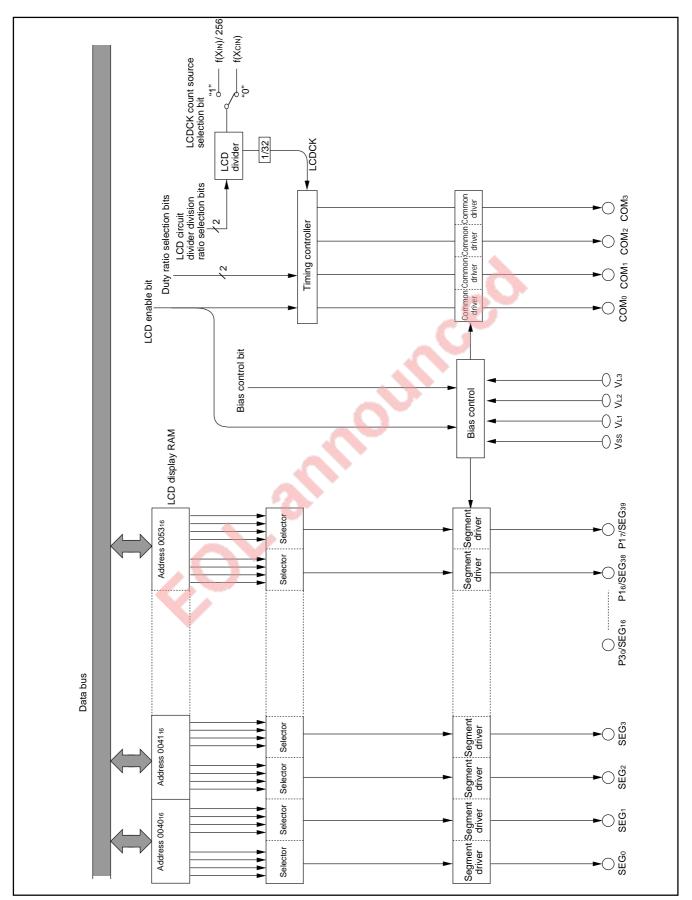

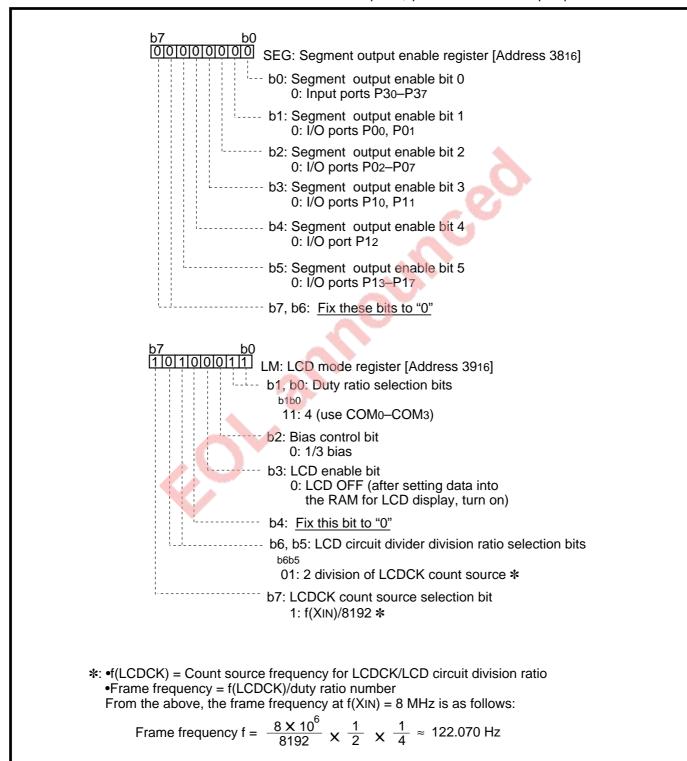

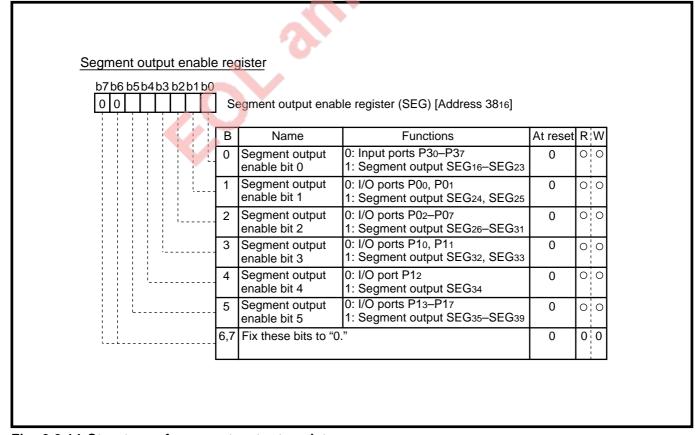

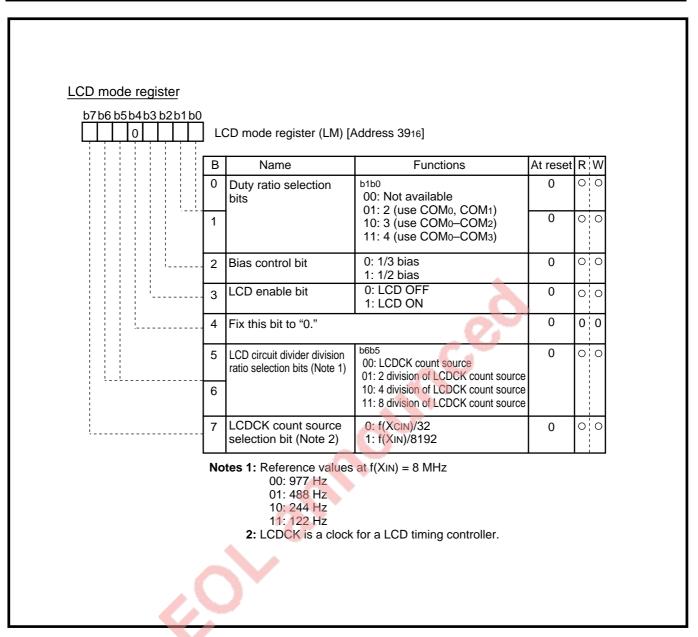

| rig. | 30 Structure of segment output enable register and LCD mode register           | 1-3∠<br>4-33             |

|      |                                                                                |                          |

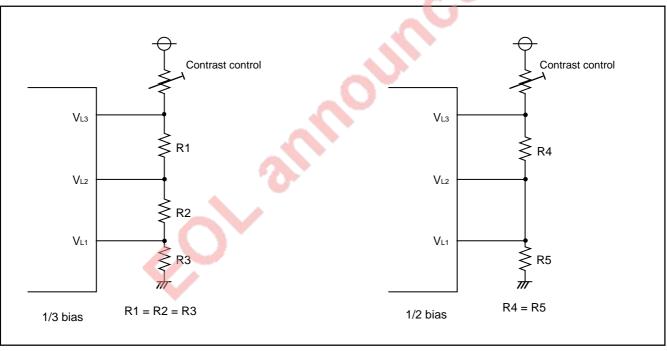

|      | 32 Example of circuit at each bias                                             |                          |

|      | 33 LCD display RAM map                                                         |                          |

|      | 34 LCD drive waveform (1/2 bias)                                               |                          |

| _    | 35 LCD drive waveform (1/3 bias)                                               |                          |

|      | 36 Watchdog timer block diagram                                                |                          |

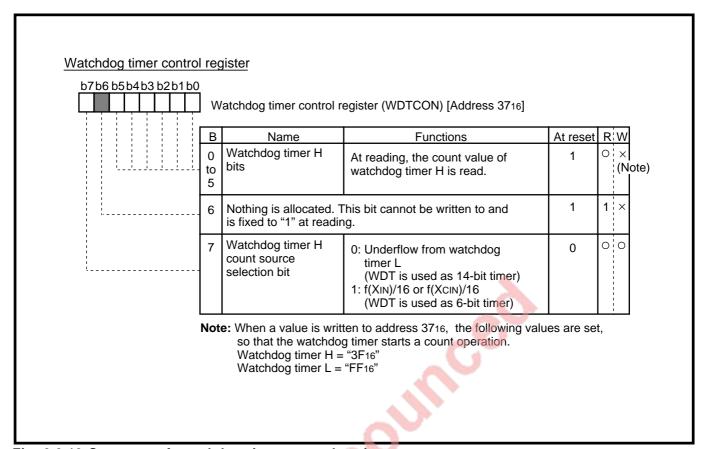

|      | 37 Structure of watchdog timer control register                                |                          |

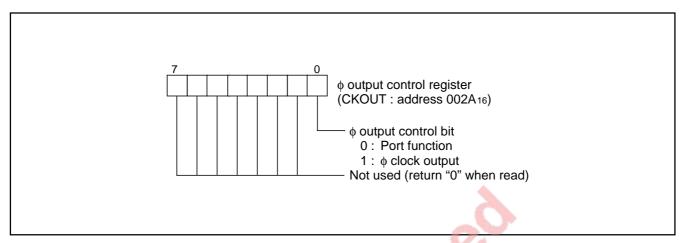

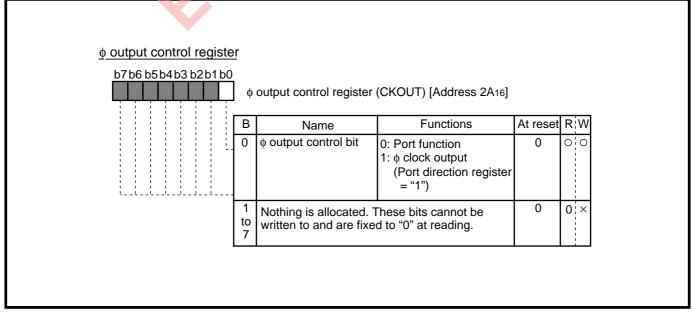

|      | 38 Structure of φ output control register                                      |                          |

|      | 39 Example of reset circuit                                                    |                          |

| _    | 40 Internal state of microcomputer immediately after reset                     |                          |

|      | 41 Reset sequence                                                              |                          |

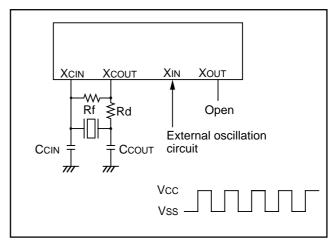

|      | 42 Ceramic resonator circuit                                                   |                          |

|      | 43 External clock input circuit                                                |                          |

| _    | 44 Clock generating circuit block diagram                                      |                          |

|      | 45 State transitions of internal clock φ                                       |                          |

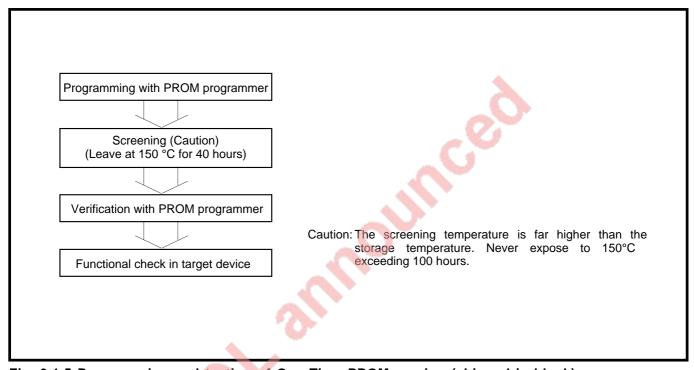

|      | 46 Programming and testing of One Time PROM version                            |                          |

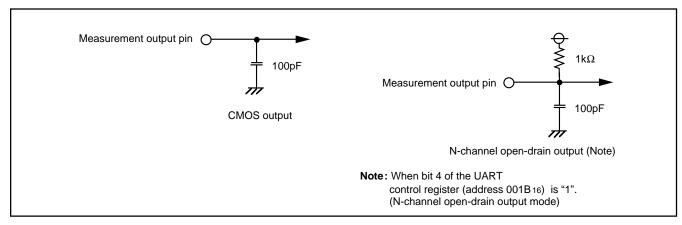

|      | 47 Circuit for measuring output switching characteristics                      |                          |

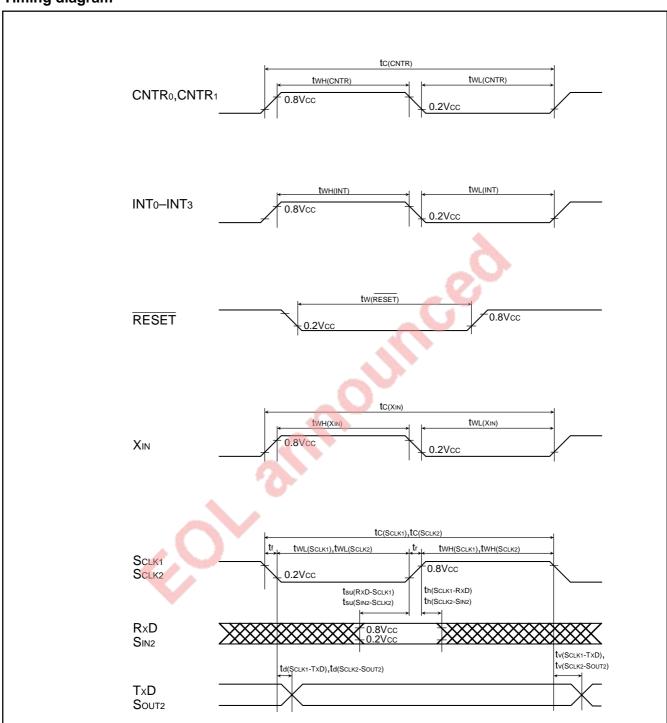

|      | 48 Timing diagram                                                              |                          |

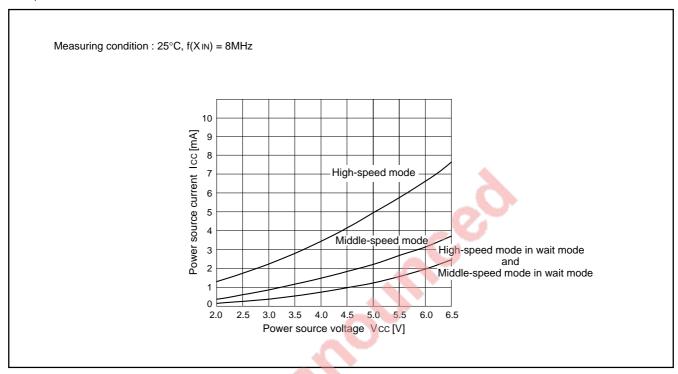

|      | 49 ICC-VCC characteristic example (f(XIN = 8 MHz))                             |                          |

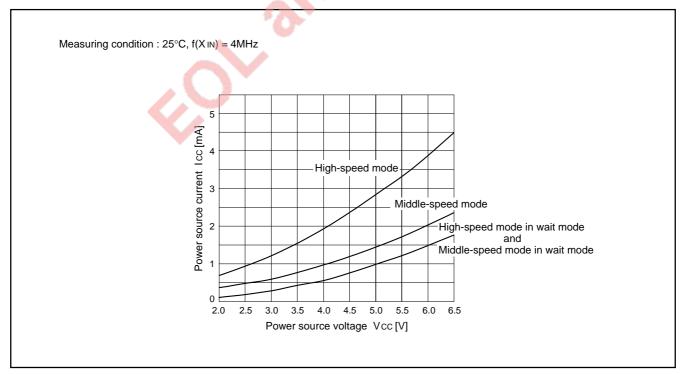

|      | 50 ICC–VCc characteristic example (f(XIN = 4 MHz))                             |                          |

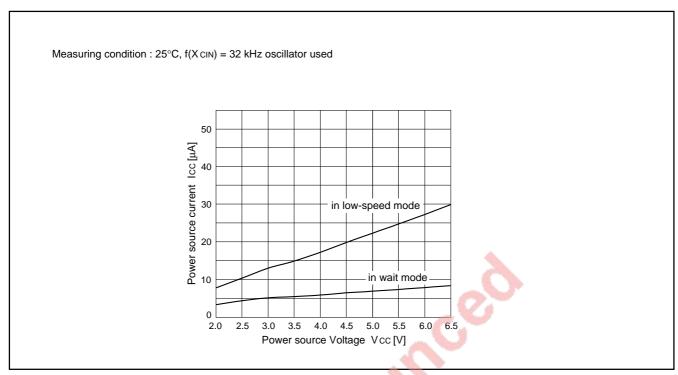

| Fig. | 51 ICC-VCC characteristic example (f(XIN) = 32 kHz, oscillator used)           | 1-67                     |

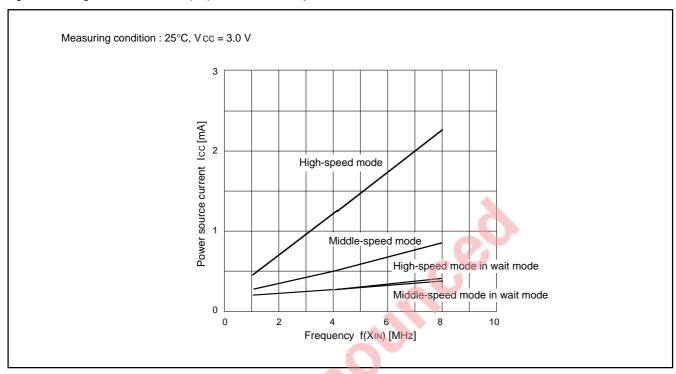

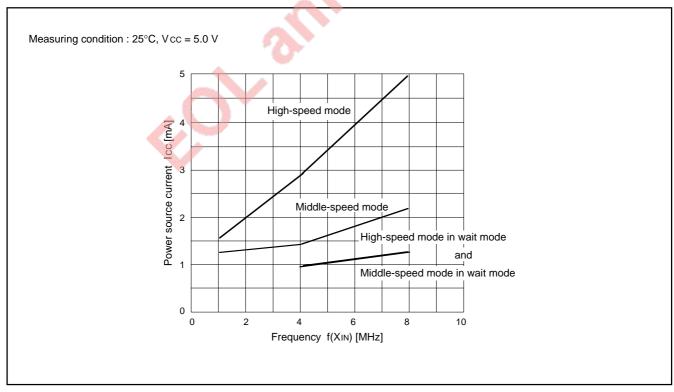

| Fig. | 52 ICC-f(XIN) characteristic example (VCC = 3.0 V)                             | 1-68                     |

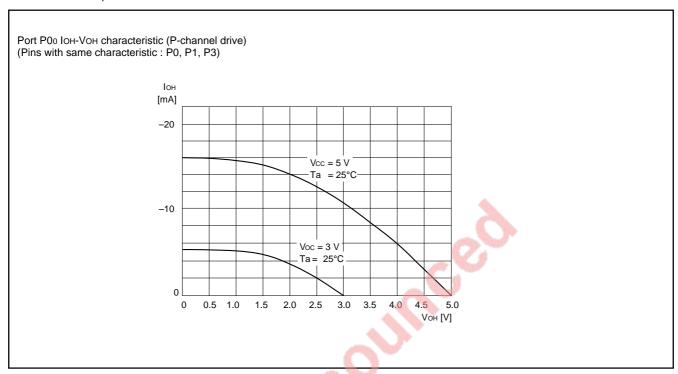

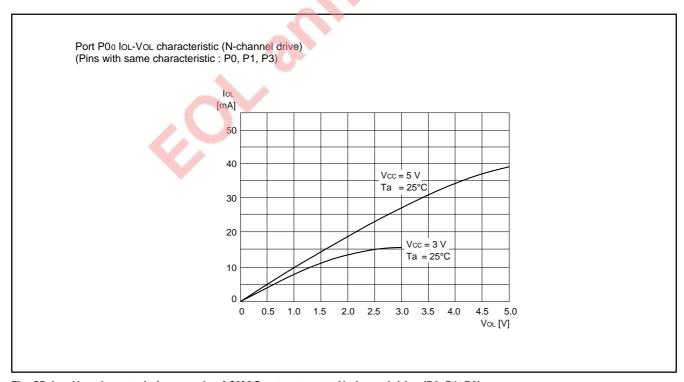

| Fig. 54 ІОН–VOH characteristic example of CMOS output port at P-channel drive (P0, P1                |             |

|------------------------------------------------------------------------------------------------------|-------------|

| Fig. 55 IOL-VOL characteristic example of CMOS output port at N-channel drive (P0, P1,               |             |

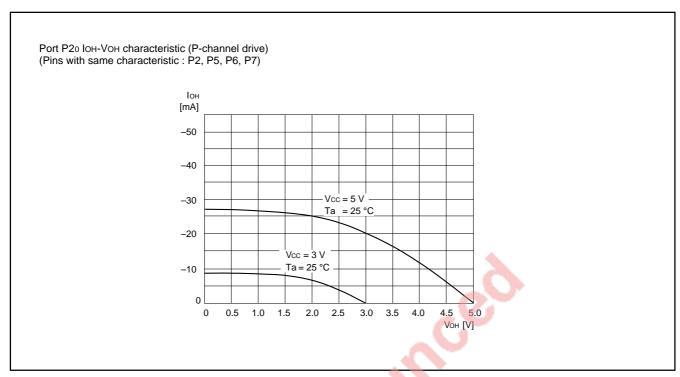

| Fig. 56 IOH–VOH characteristic example of CMOS output port at P-channel drive (P2, P5, P             |             |

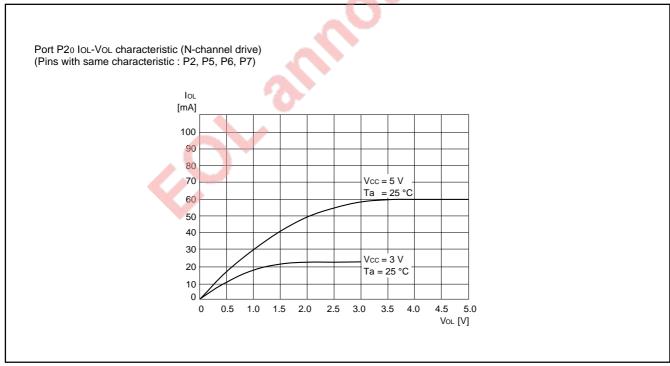

| Fig. 57 IOL-VOL characteristic example of CMOS output port at N-channel drive (P2, P5, P6            | 6, P7) 1-70 |

| CHAPTER 2. APPLICATION                                                                               |             |

|                                                                                                      |             |

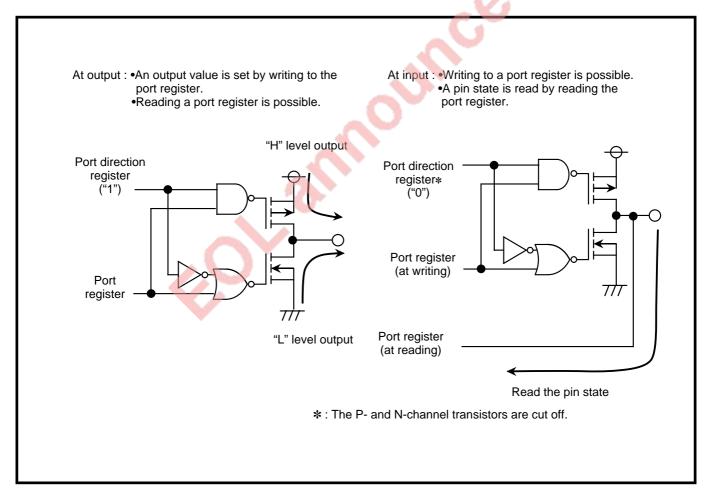

| Fig. 2.1.1 I/O port write and read                                                                   |             |

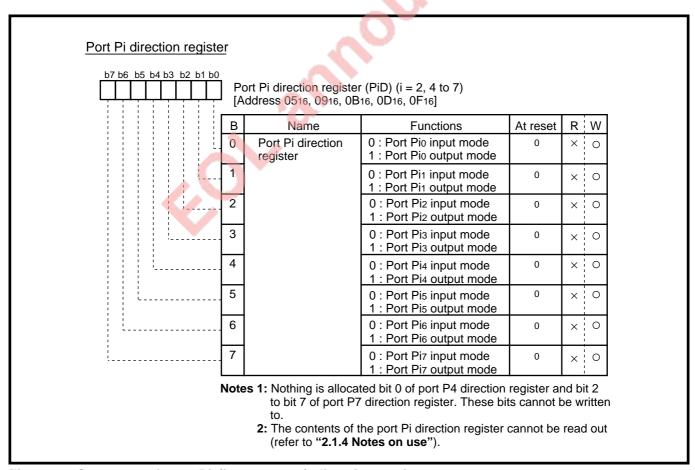

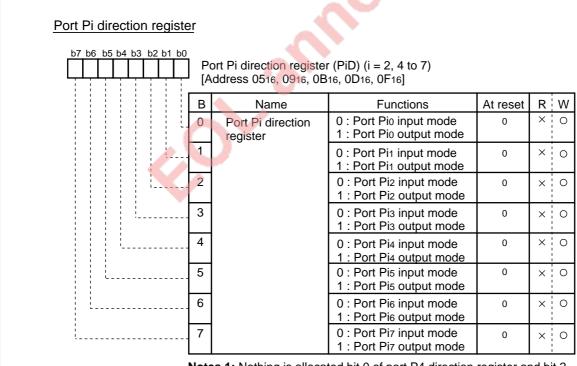

| Fig. 2.1.2 Structure of port Pi (i = 2, 4 to 7) direction register                                   |             |

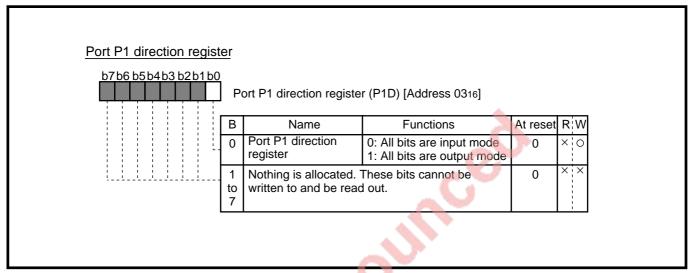

| Fig. 2.1.3 Structure of ports P0 and P1 direction registers                                          |             |

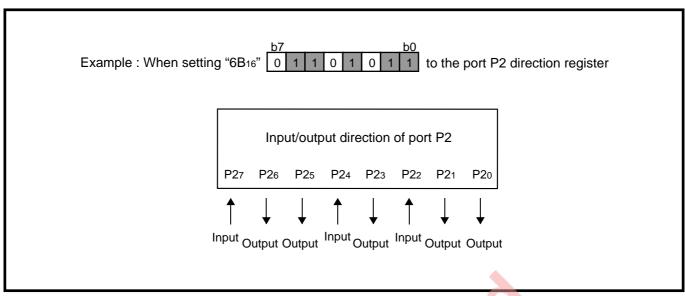

| Fig. 2.1.4 Port direction register setting example                                                   |             |

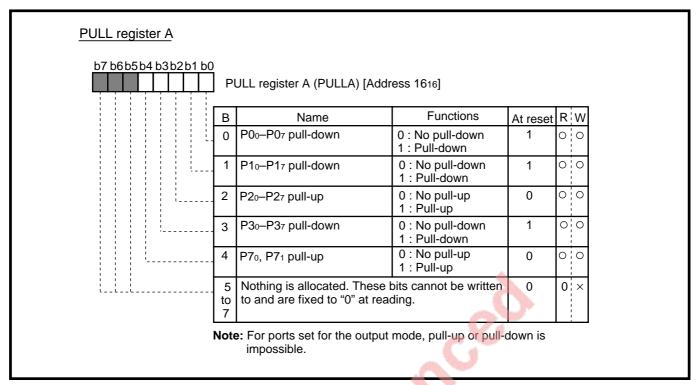

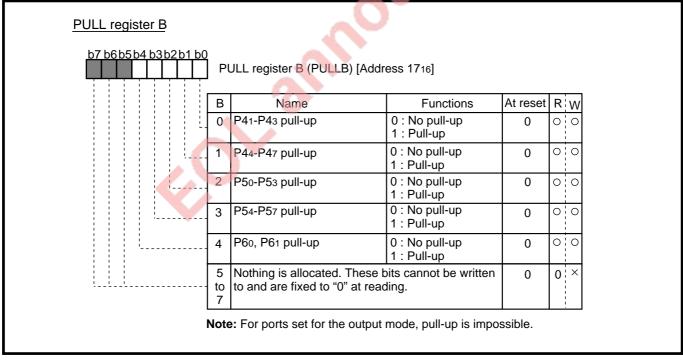

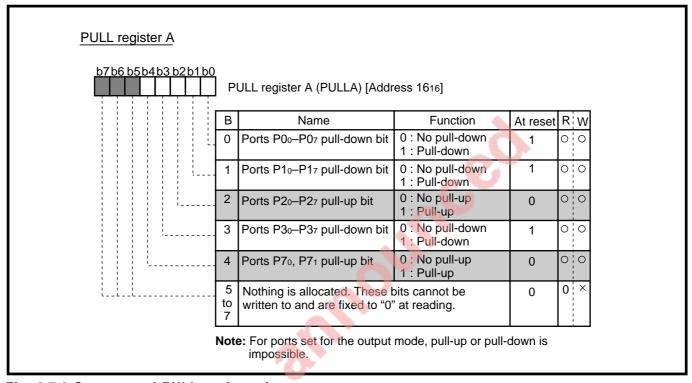

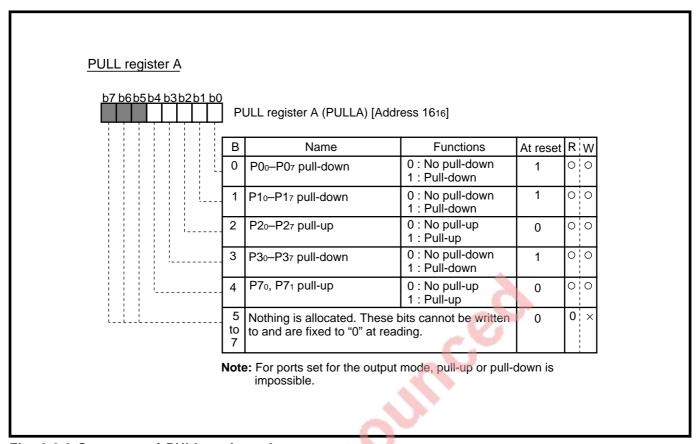

| Fig. 2.1.5 Structure of PULL register A                                                              |             |

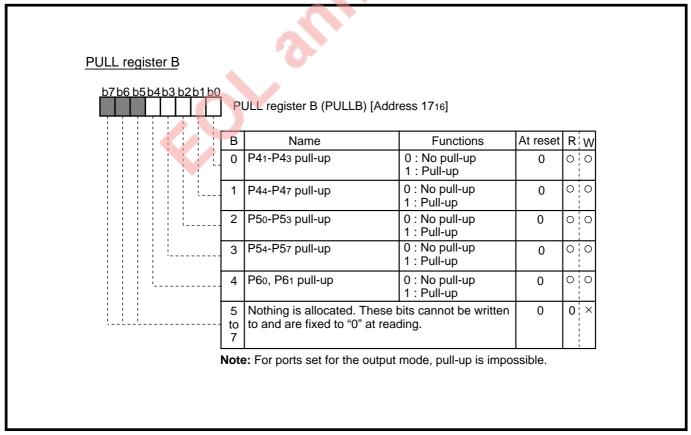

| Fig. 2.1.6 Structure of PULL register B                                                              |             |

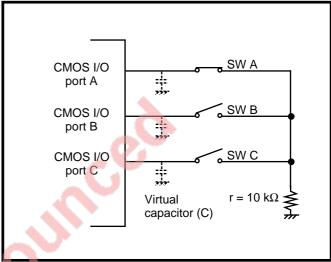

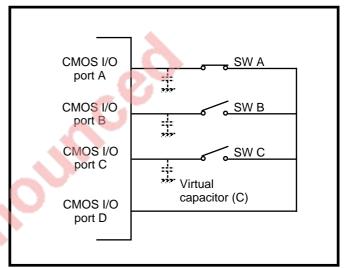

| Fig. 2.1.7 Connection example 1 for key input                                                        |             |

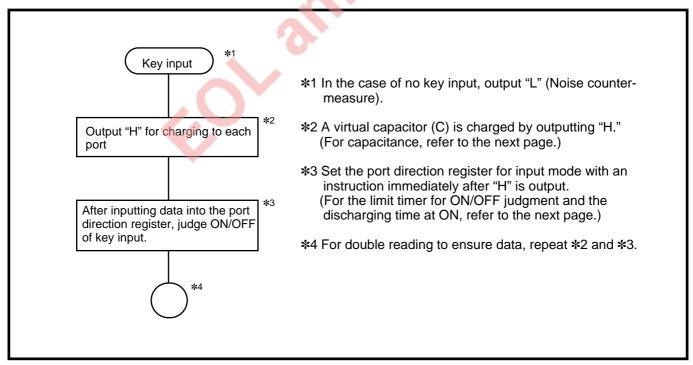

| Fig. 2.1.8 Key input control procedure 1                                                             |             |

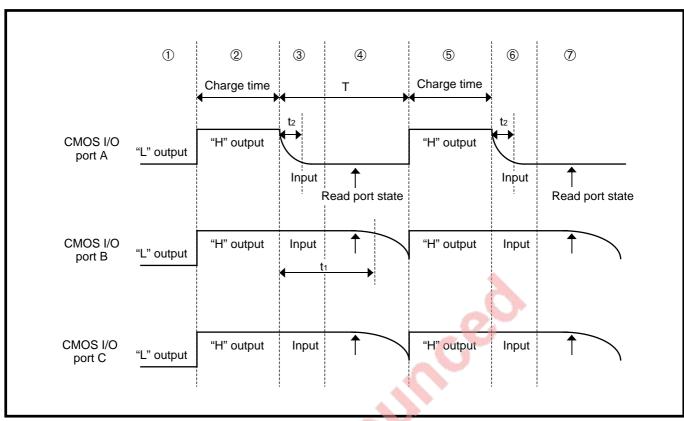

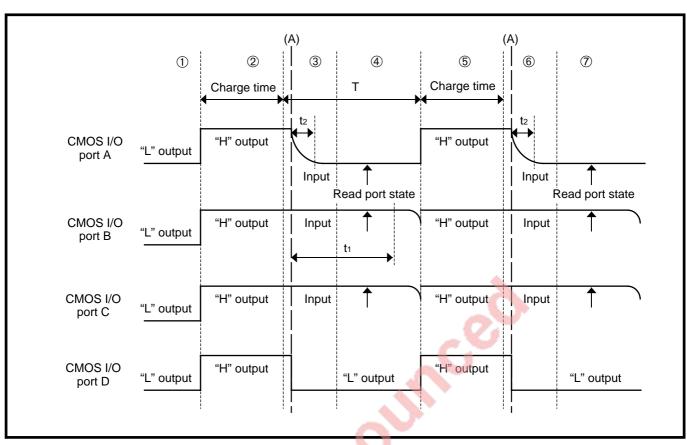

| Fig. 2.1.9 Timing diagram 1 where switch A is pressed                                                |             |

| Fig. 2.1.10 Connection example 2 for key input                                                       |             |

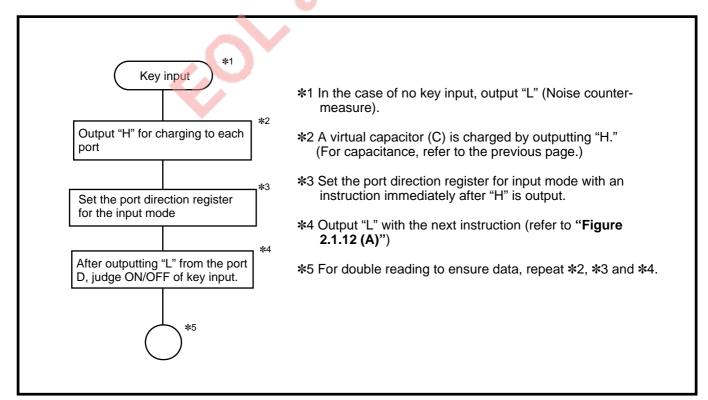

| Fig. 2.1.11 Key input control procedure 2                                                            |             |

| Fig. 2.1.12 Timing diagram 2 where switch A is pressed                                               |             |

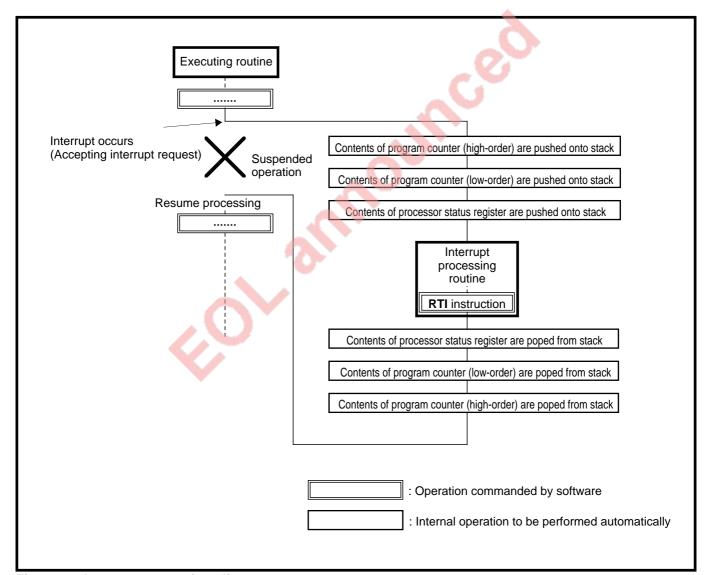

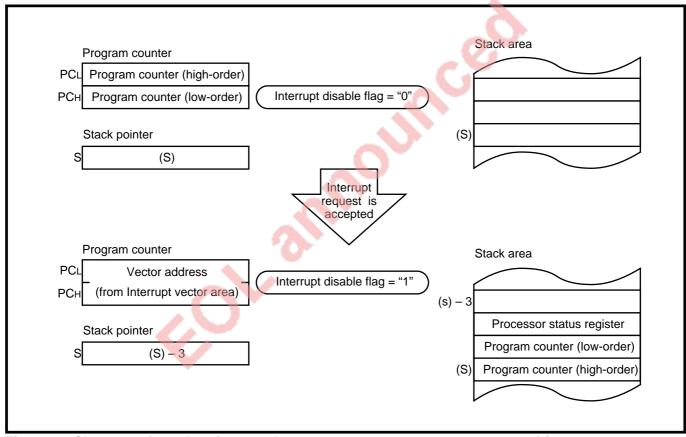

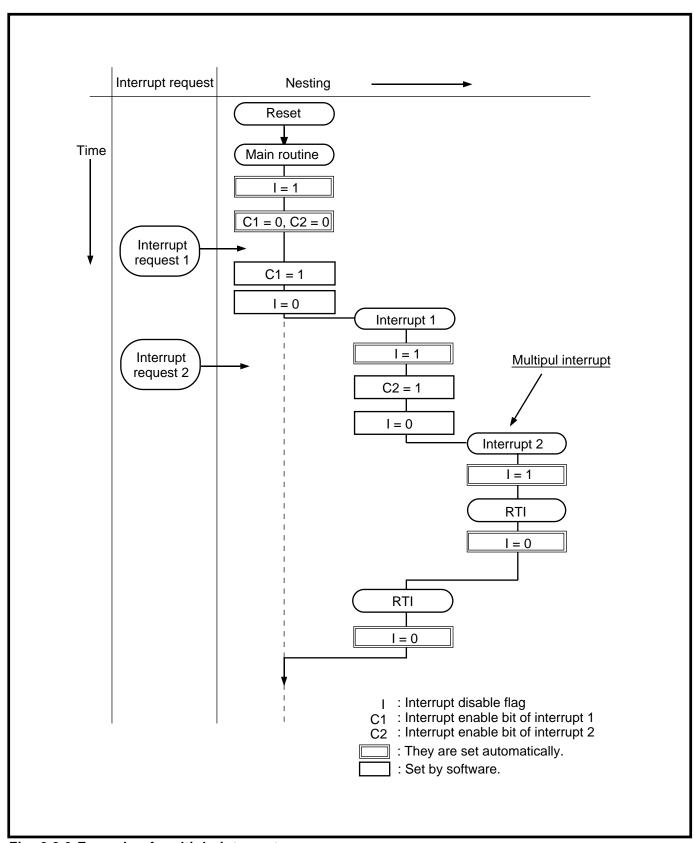

| Fig. 2.2.1 Interrupt operation diagram                                                               |             |

| Fig. 2.2.2 Changes of stack pointer and program counter upon acceptance of interrupt re              | •           |

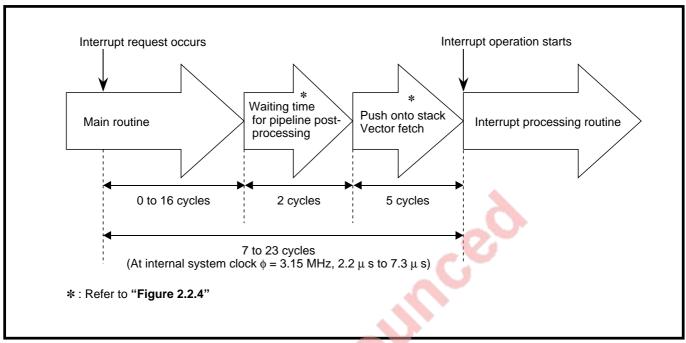

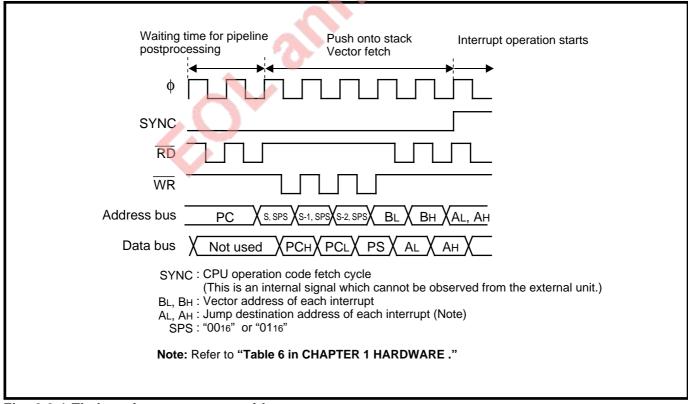

| Fig. 2.2.3 Processing time up to execution of interrupt processing routine                           |             |

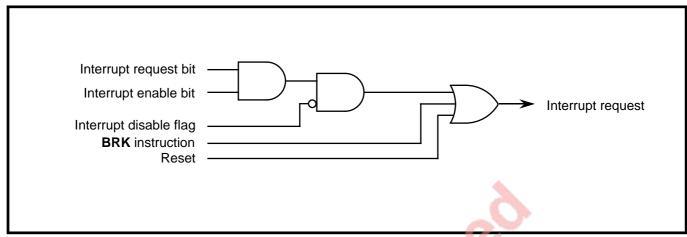

| Fig. 2.2.5 Interrupt control diagram                                                                 |             |

| Fig. 2.2.6 Example of multiple interrupts                                                            |             |

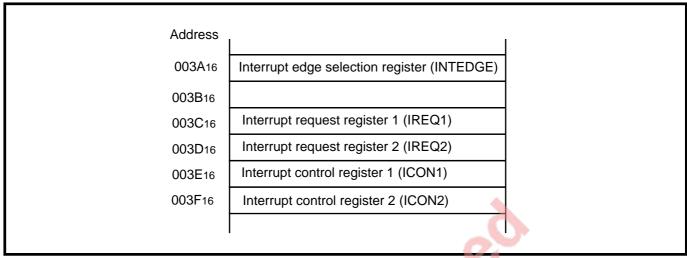

| Fig. 2.2.7 Memory allocation of interrupt-related registers                                          |             |

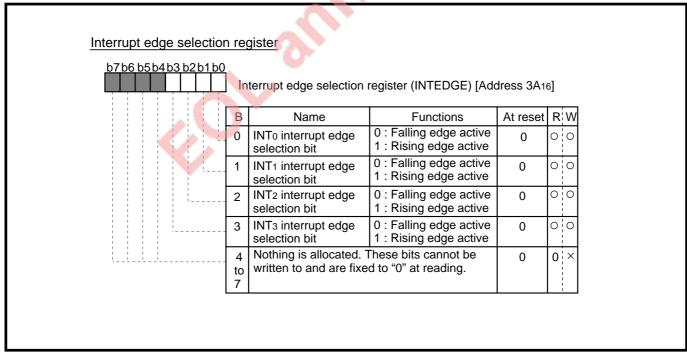

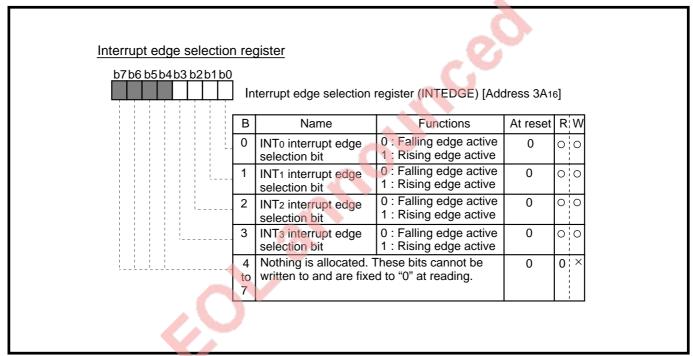

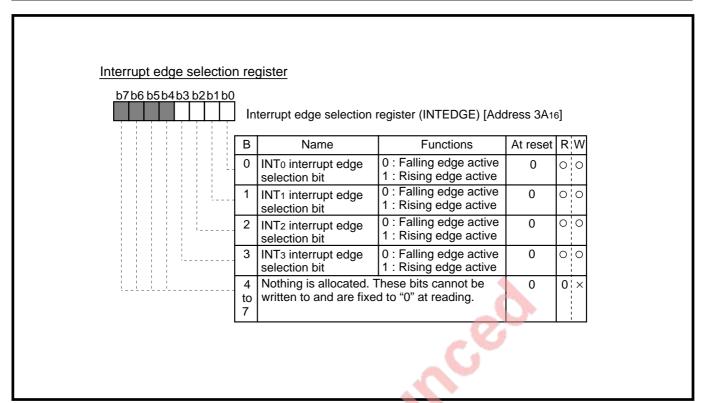

| Fig. 2.2.8 Structure of interrupt edge selection register                                            |             |

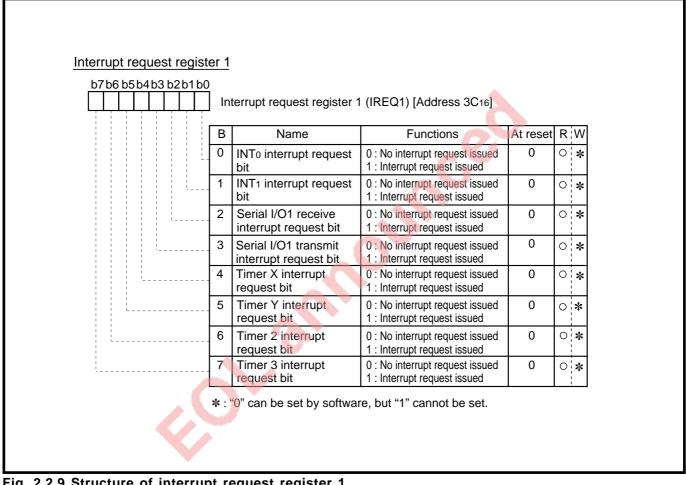

| Fig. 2.2.9 Structure of interrupt request register 1                                                 |             |

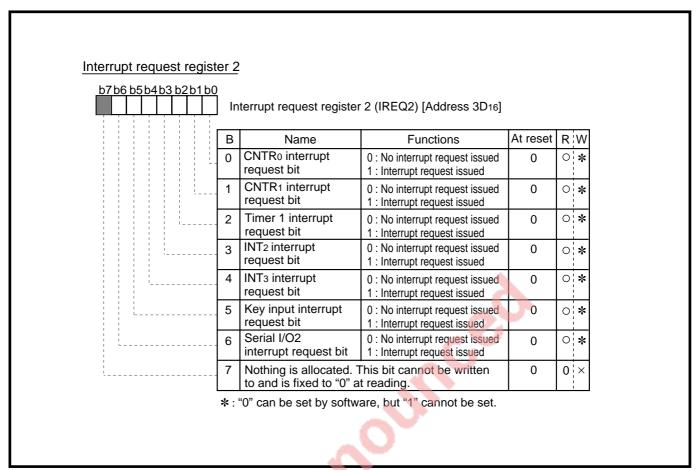

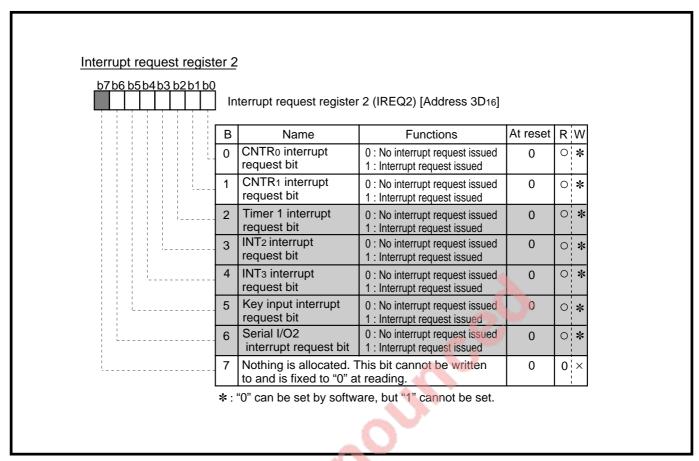

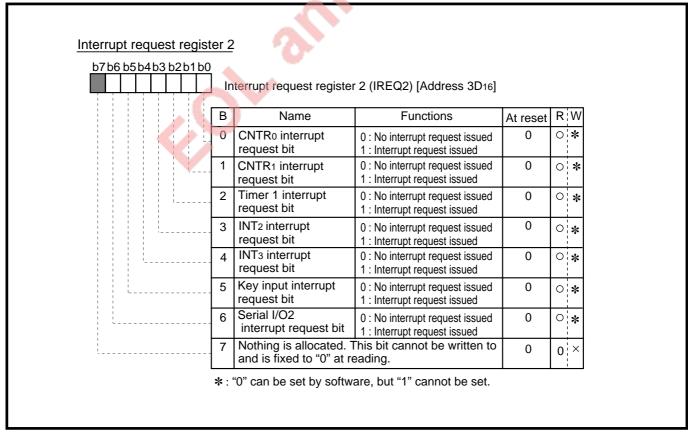

| Fig. 2.2.10 Structure of interrupt request register 2                                                |             |

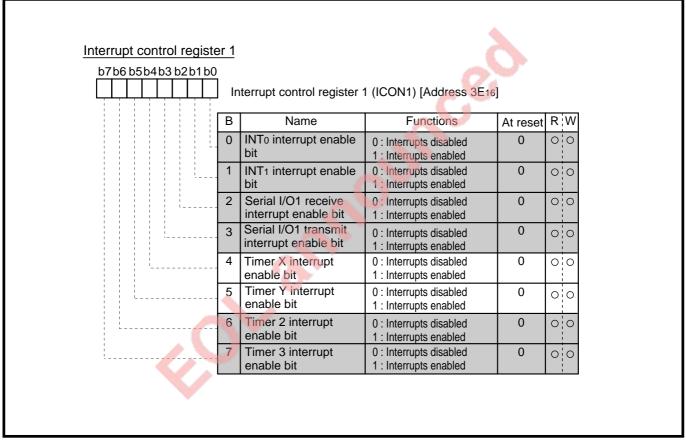

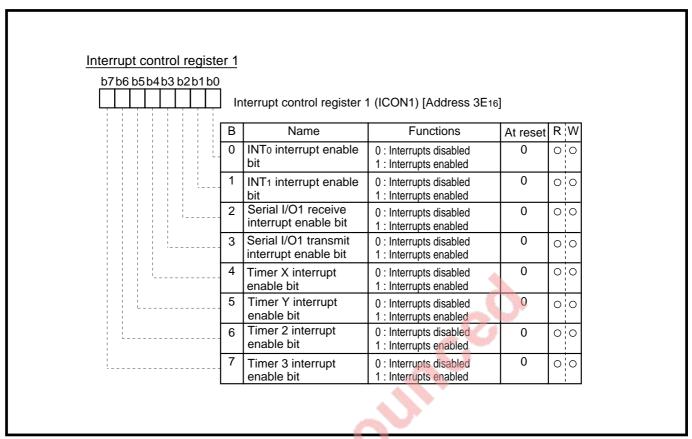

| Fig. 2.2.11 Structure of interrupt control register 1                                                |             |

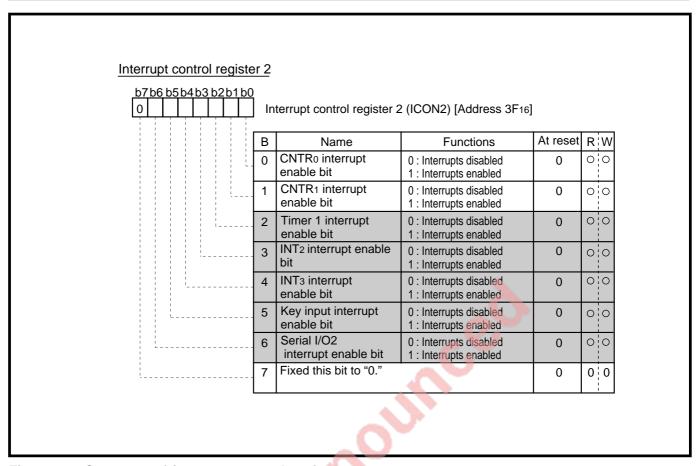

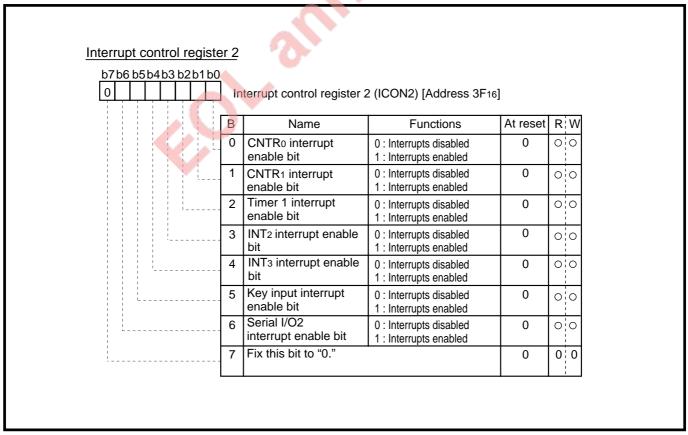

| Fig. 2.2.12 Structure of interrupt control register 2                                                |             |

| Fig. 2.2.13 Structure of processor status register                                                   |             |

| Fig. 2.2.14 Structure of interrupt edge selection register                                           |             |

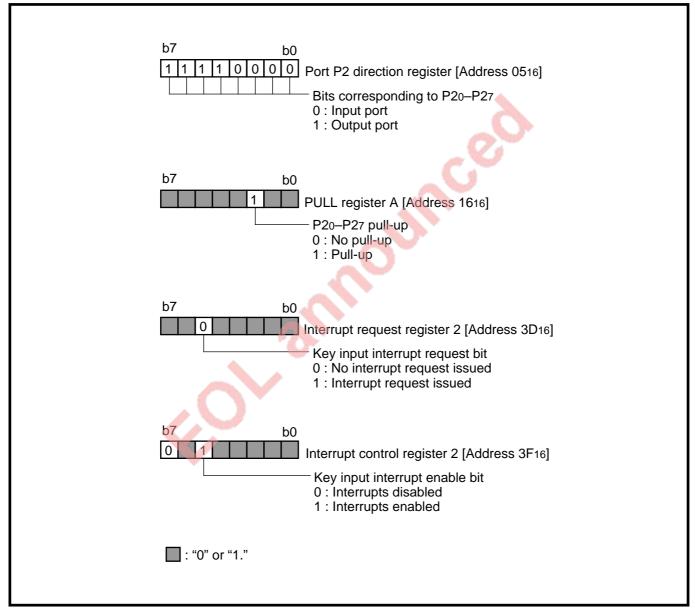

| Fig. 2.2.15 Connection example when key input interrupt is used, and port P2 block diagram           |             |

| Fig. 2.2.16 Setting values (corresponding to Figure 2.2.15) of key input interrupt-related registers |             |

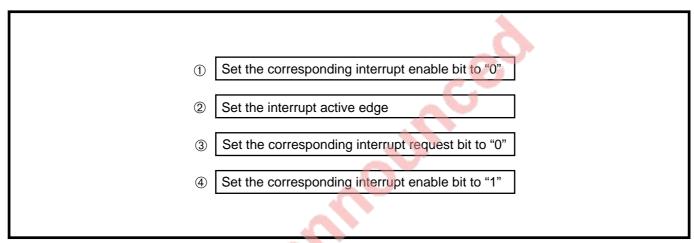

| Fig. 2.2.17 Register setting example                                                                 | 2-31        |

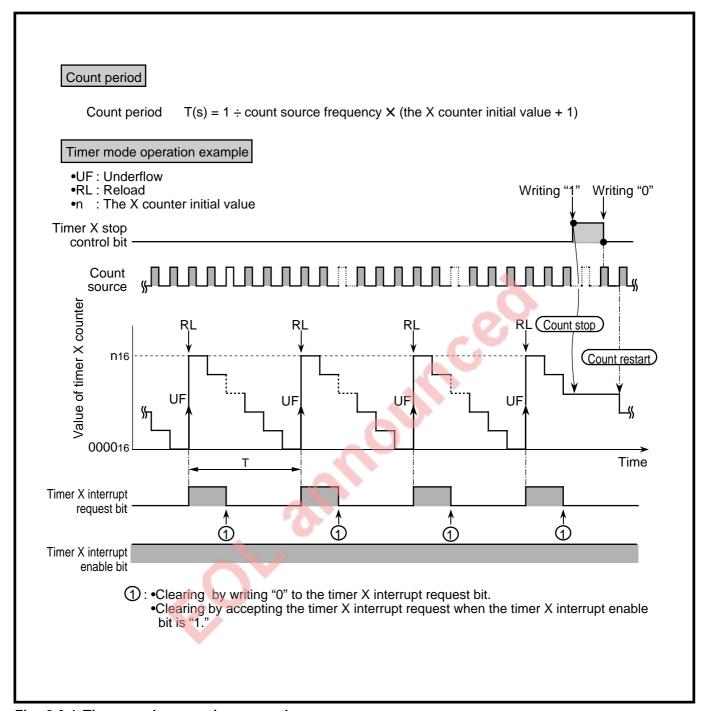

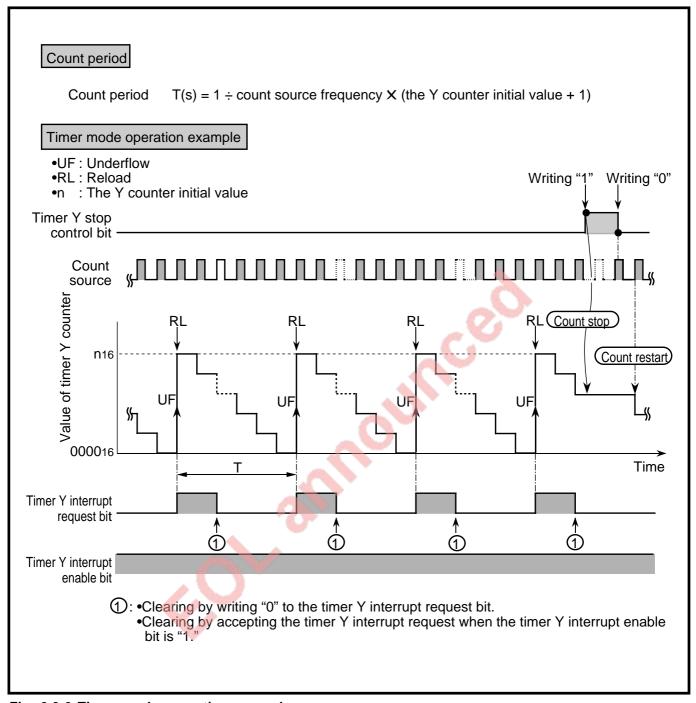

| Fig. 2.3.1 Timer mode operation example                                                              | 2-33        |

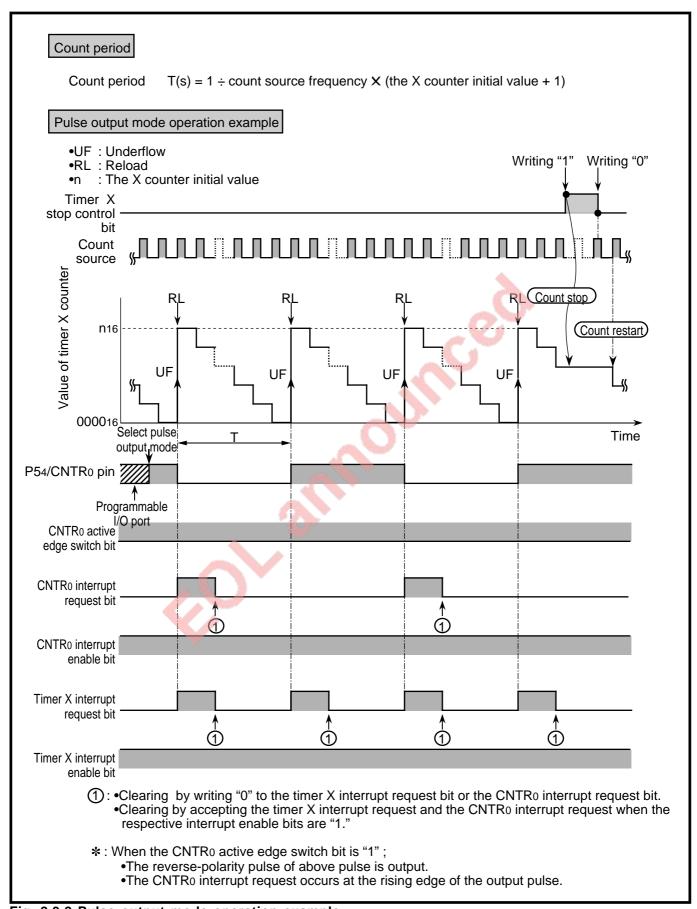

| Fig. 2.3.2 Pulse output mode operation example                                                       | 2-35        |

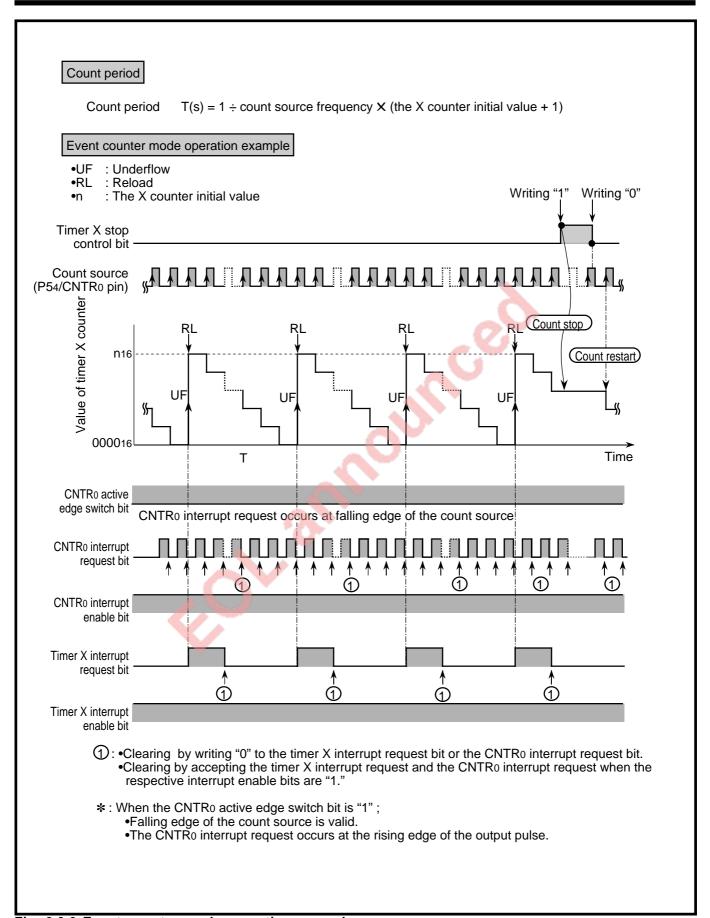

| Fig. 2.3.3 Event counter mode operation example                                                      | 2-37        |

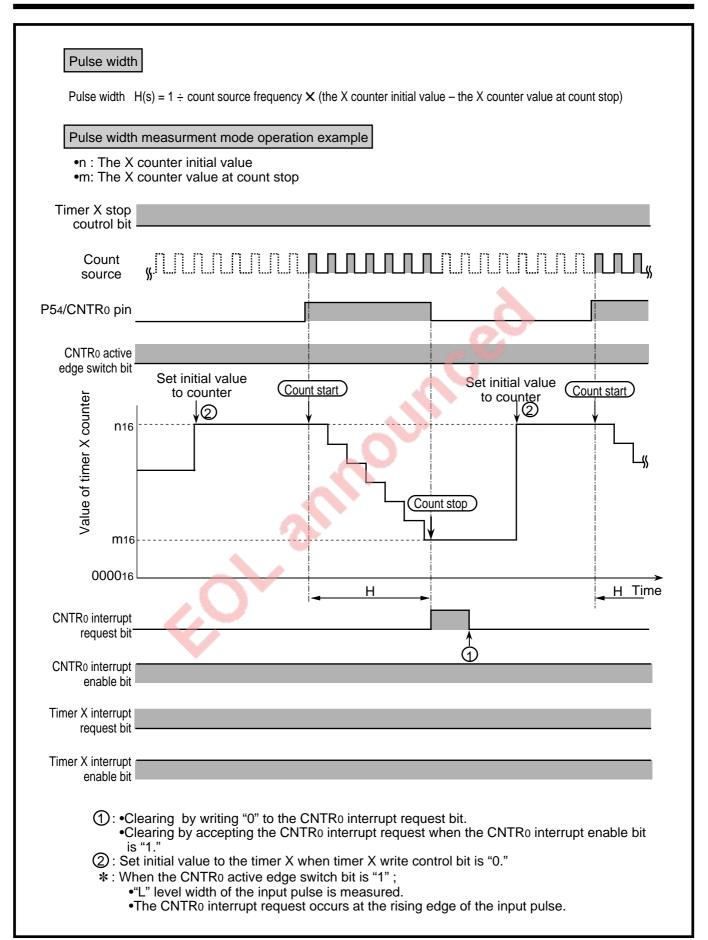

| Fig. 2.3.4 Pulse width measurement mode operation example                                            |             |

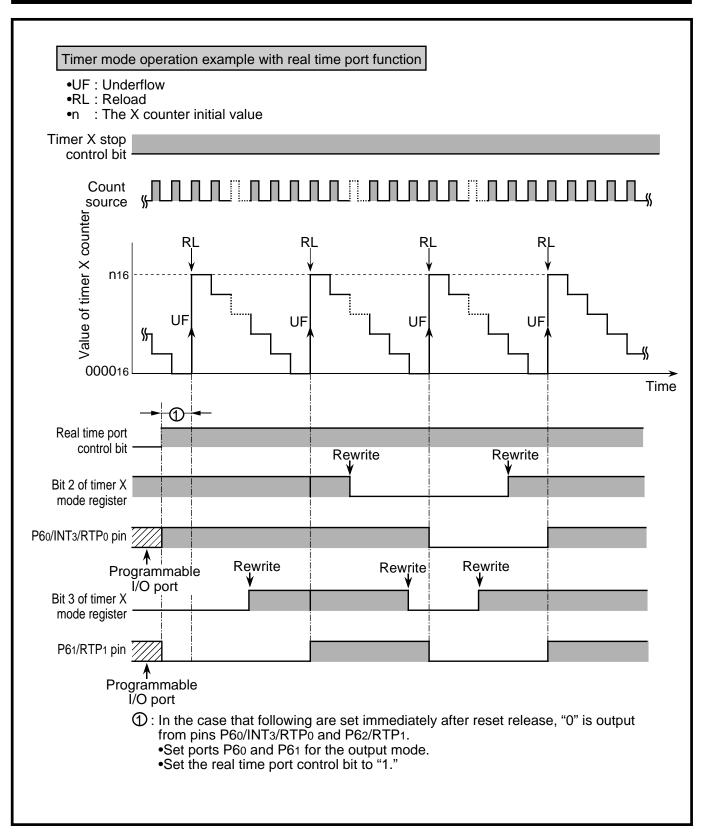

| Fig. 2.3.5 Timer mode operation example with real time port function                                 |             |

| Fig. 2.3.6 Timer mode operation example                                                              |             |

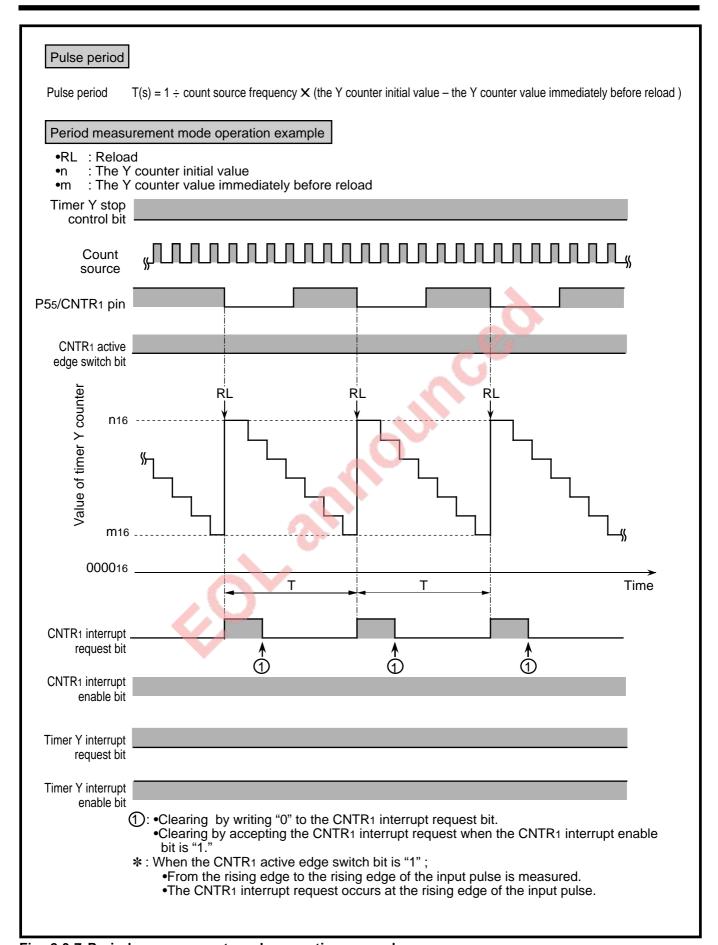

| Fig. 2.3.7 Period measurement mode operation example                                                 |             |

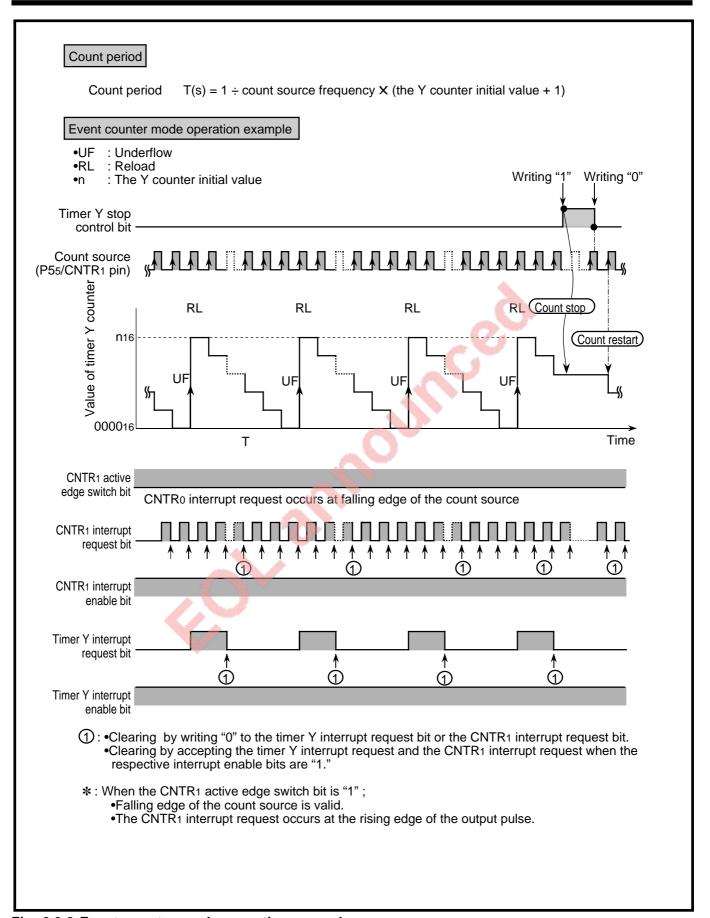

| Fig. 2.3.8 Event counter mode operation example                                                      |             |

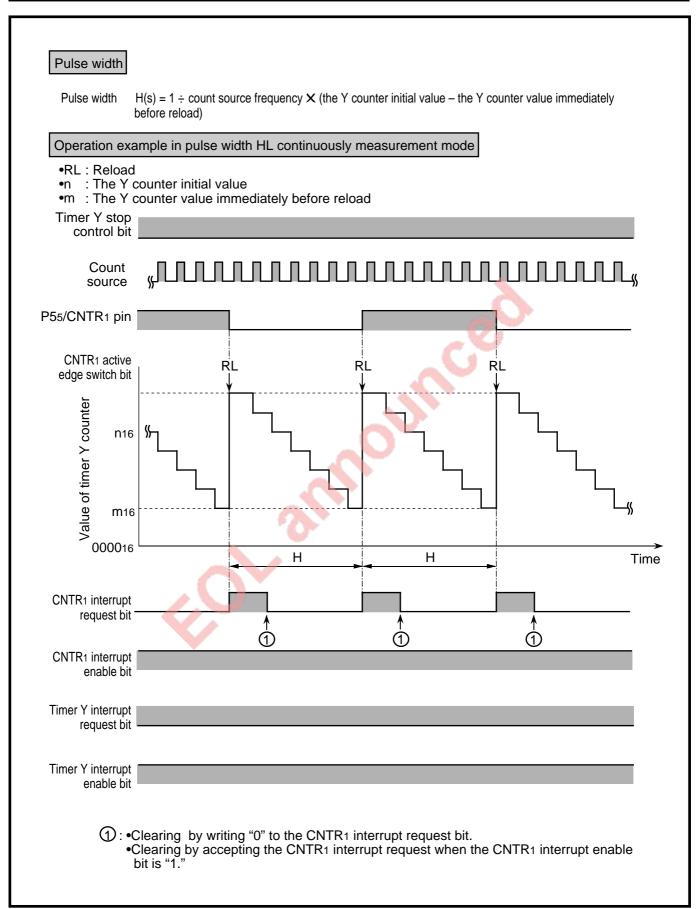

| Fig. 2.3.9 Pulse width HL continuously measurement mode operation example                            |             |

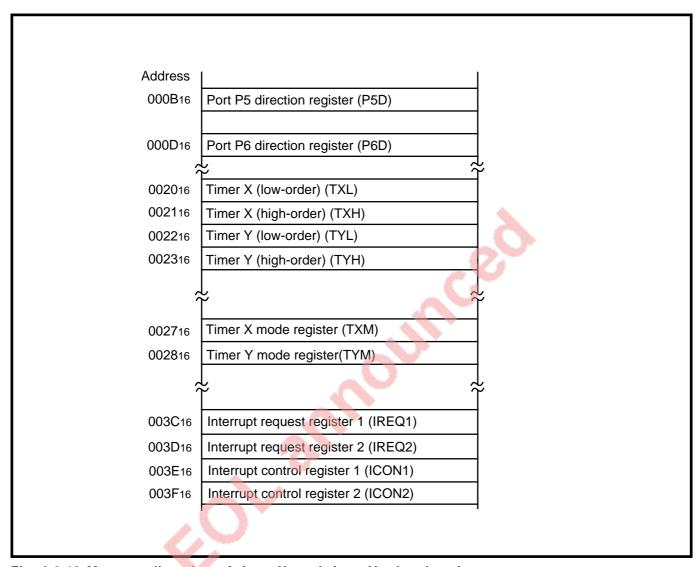

| Fig. 2.3.10 Memory allocation of timer X- and the timer Y-related registers                          |             |

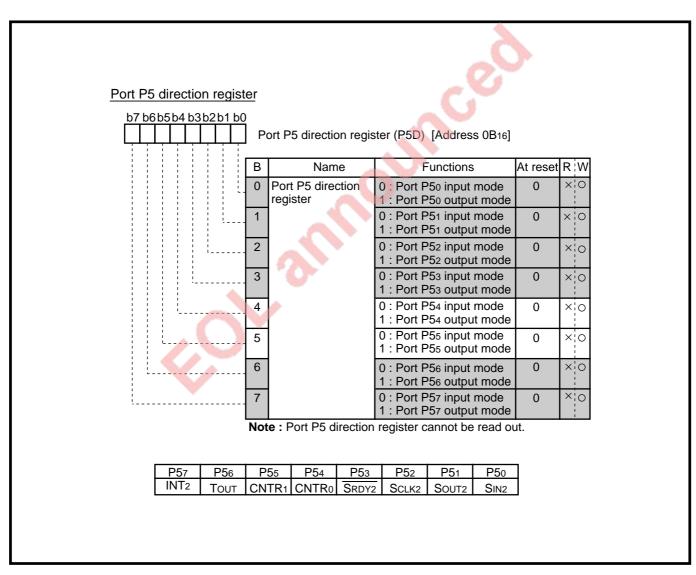

| Fig. 2.3.11 Structure of port P5 direction register                                                  |             |

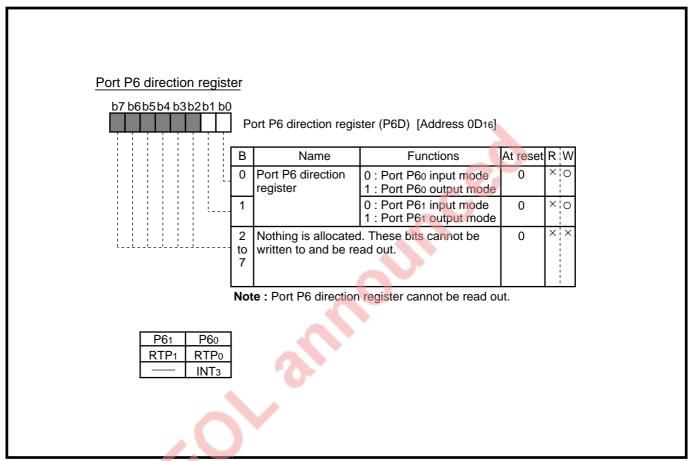

| Fig. 2.3.12 Structure of port P6 direction register                                                  |             |

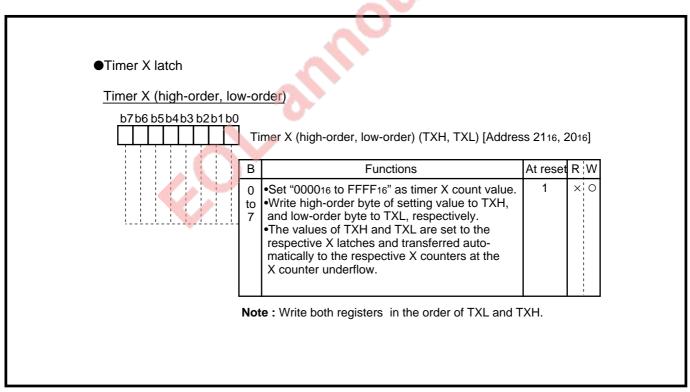

| Fig. 2.3.13 Structure of timer X latch                                                               |             |

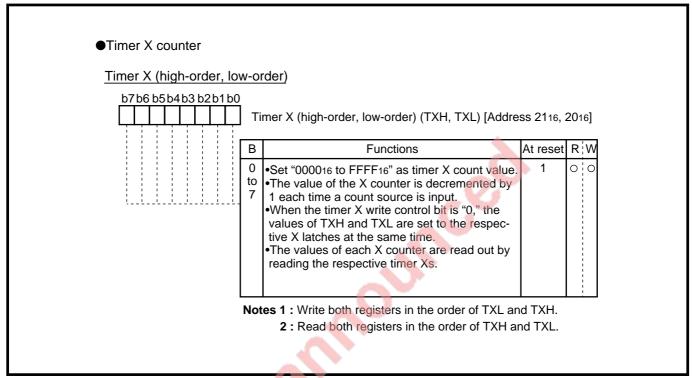

| Fig. 2.3.14 Structure of timer X counter                                                             |             |

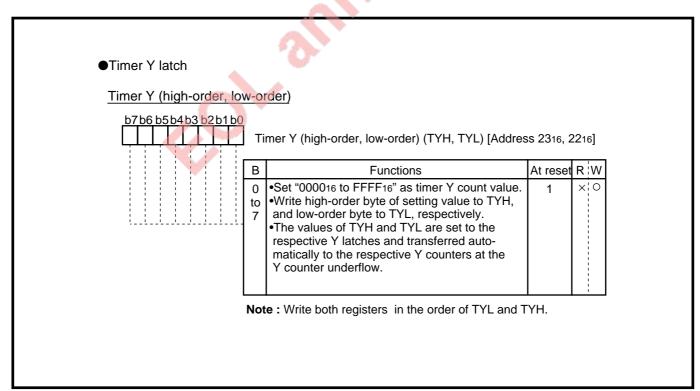

| Fig. 2.3.16 Structure of timer Y latch                                                               |             |

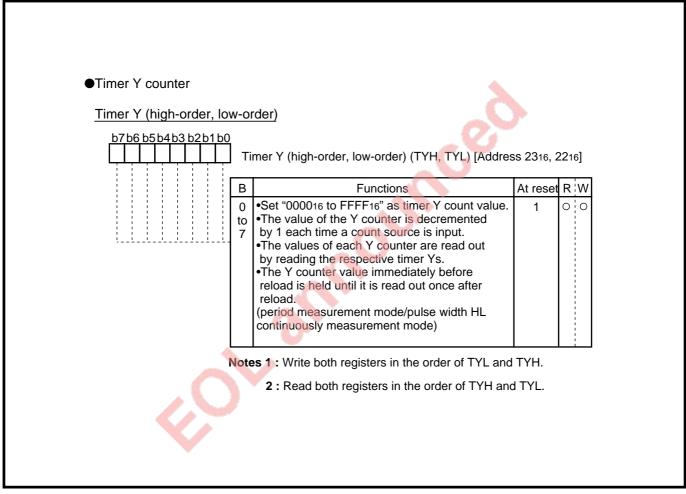

| Fig. 2.3.16 Structure of timer Y counter                                                             |             |

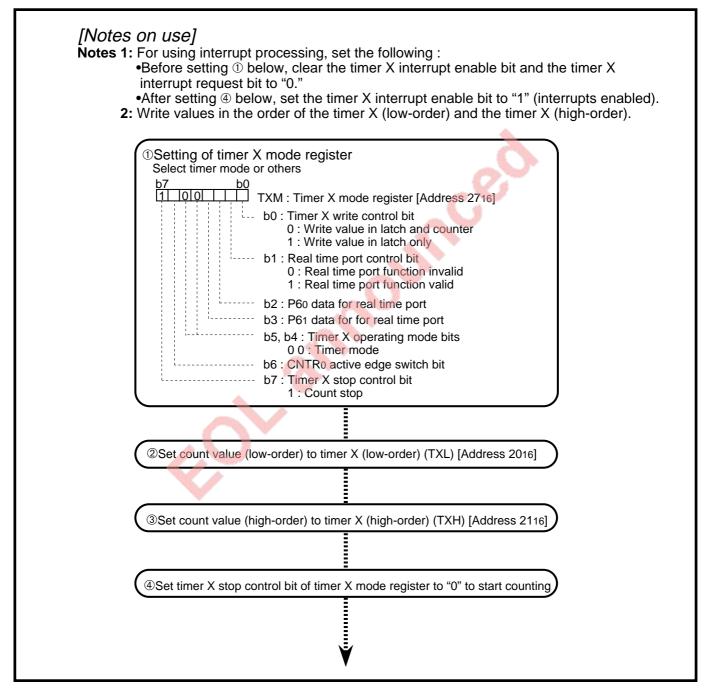

| Fig. 2.3.17 Structure of timer X mode register                                                       |             |

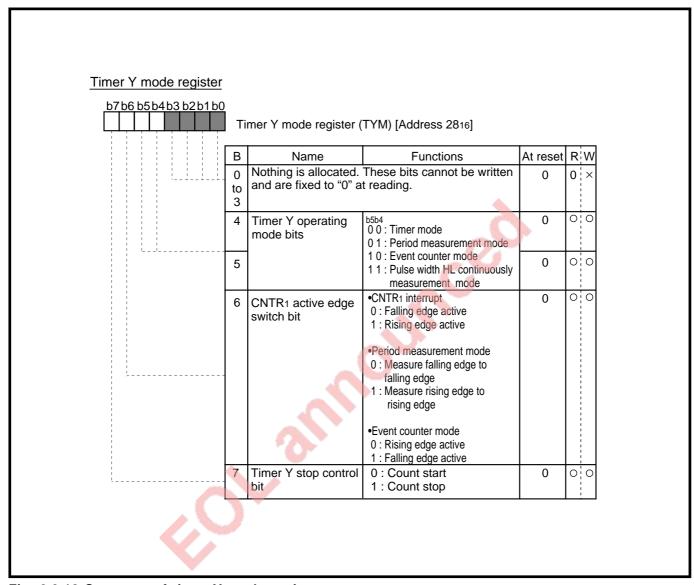

| Fig. 2.3.18 Structure of timer Y mode register                                                       |             |

| Fig. 2.3.19 Structure of interrupt request register 1                                                |             |

| Fig. 2.3.20 Structure of interrupt request register 2                                                |             |

| Fig. 2.3.21 Structure of interrupt control register 1                                                | ∠-04        |

# List of figures

| Fig. 2.3.22 Structure of interrupt control register 2                                           |       |

|-------------------------------------------------------------------------------------------------|-------|

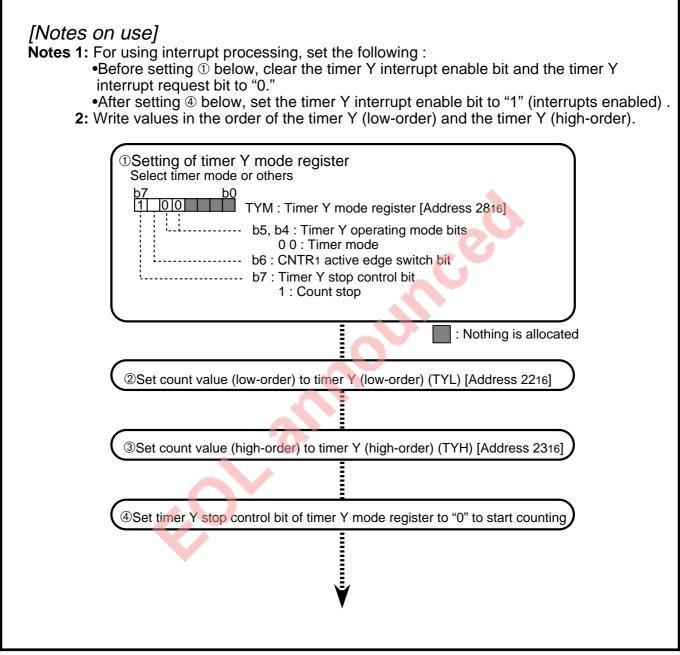

| Fig. 2.3.23 Example of setting registers for using timer mode                                   | 2-66  |

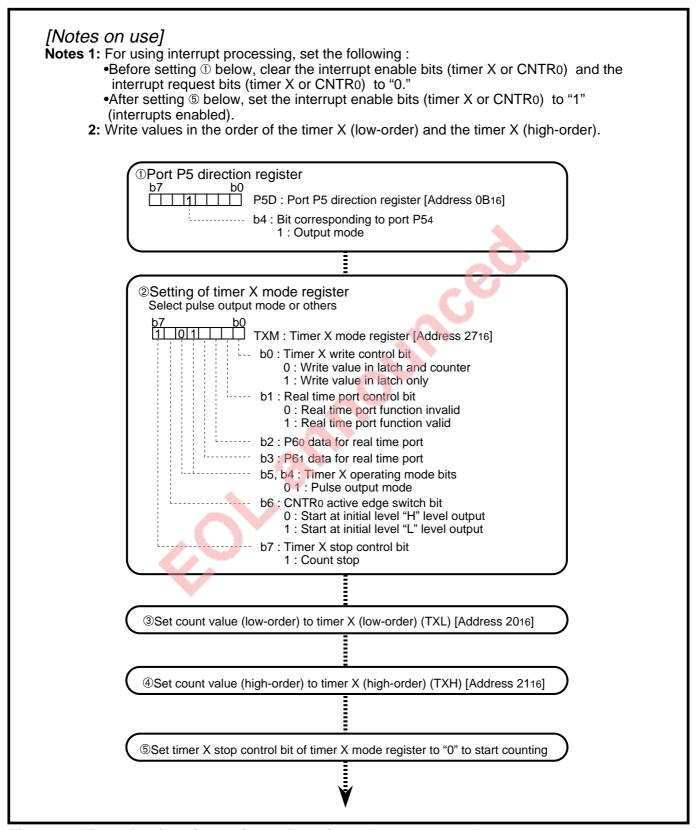

| Fig. 2.3.24 Example of setting registers for using pulse output mode                            | 2-67  |

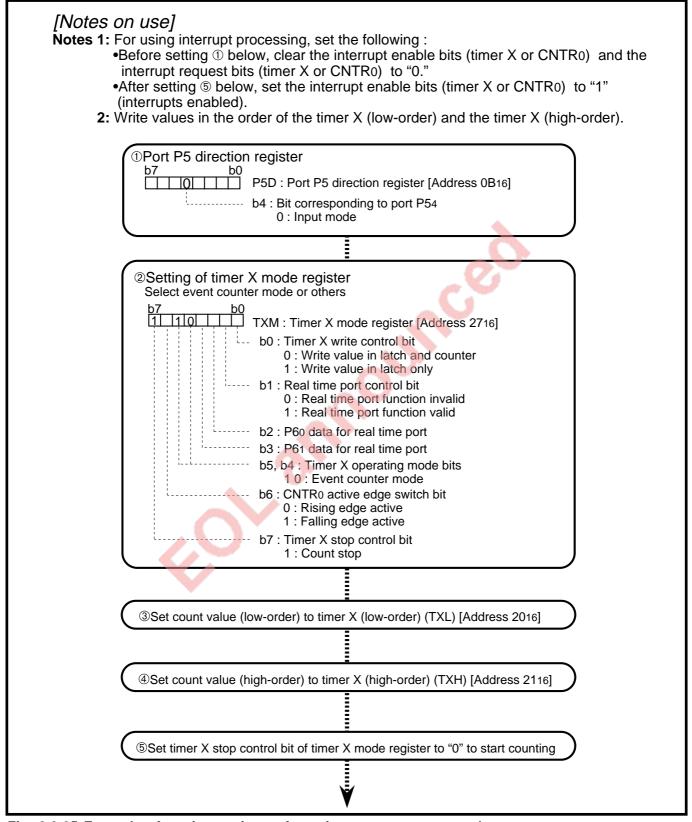

| Fig. 2.3.25 Example of setting registers for using event counter mode                           | 2-68  |

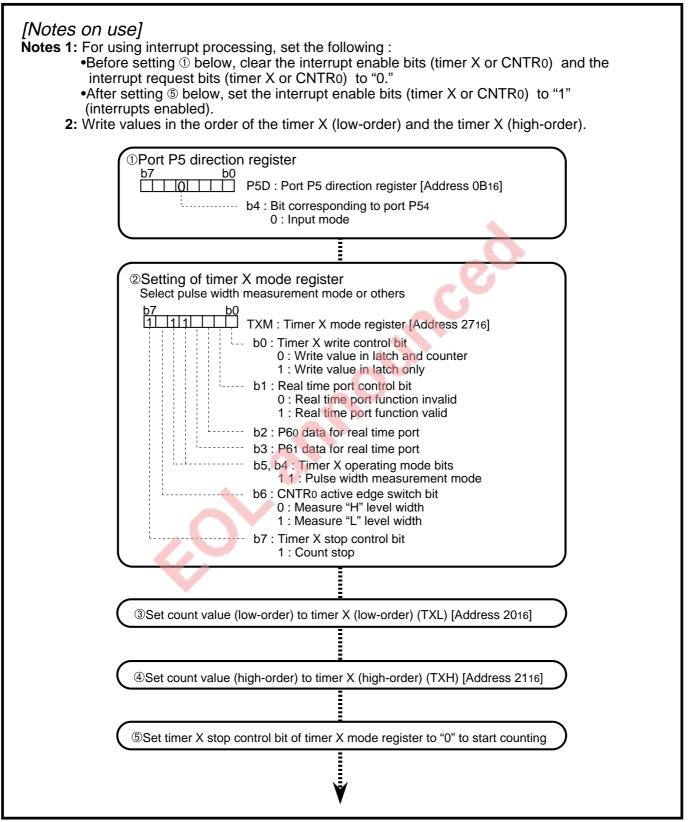

| Fig. 2.3.26 Example of setting registers for using pulse width measurement mode                 |       |

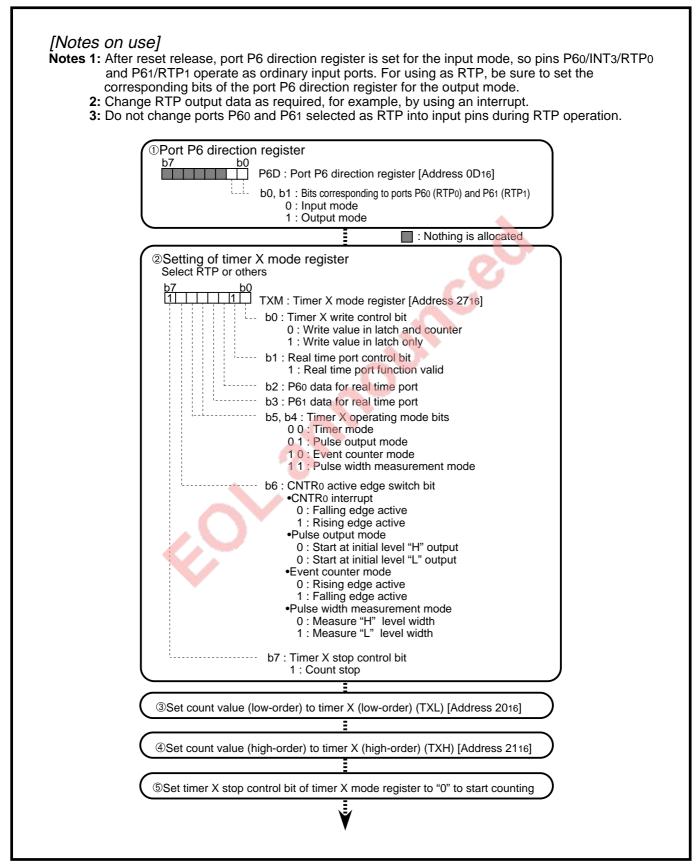

| Fig. 2.3.27 Example of setting registers for using RTP                                          |       |

| Fig. 2.3.28 Example of setting registers for using timer mode                                   |       |

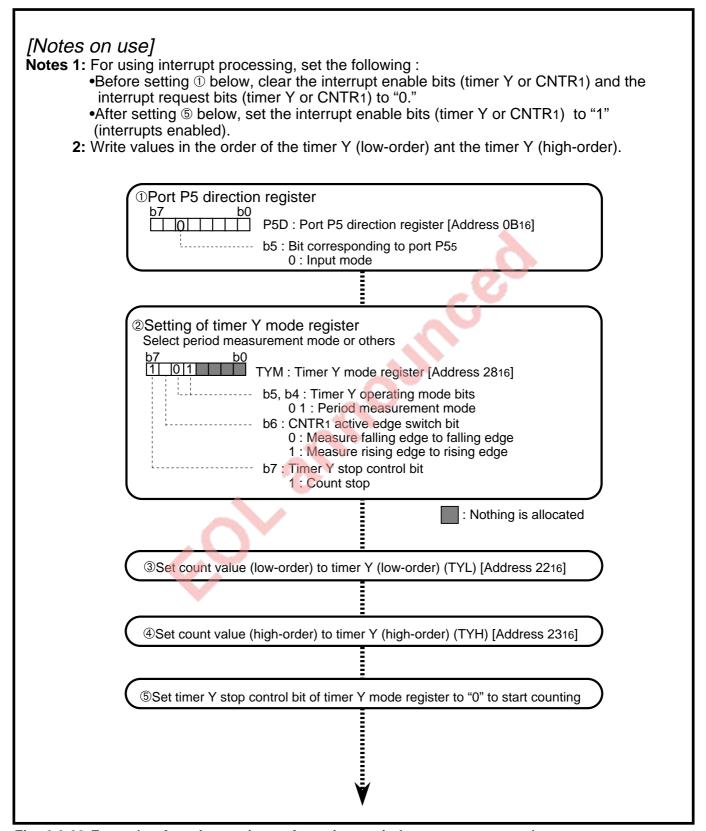

| Fig. 2.3.29 Example of setting registers for using period measurement mode                      |       |

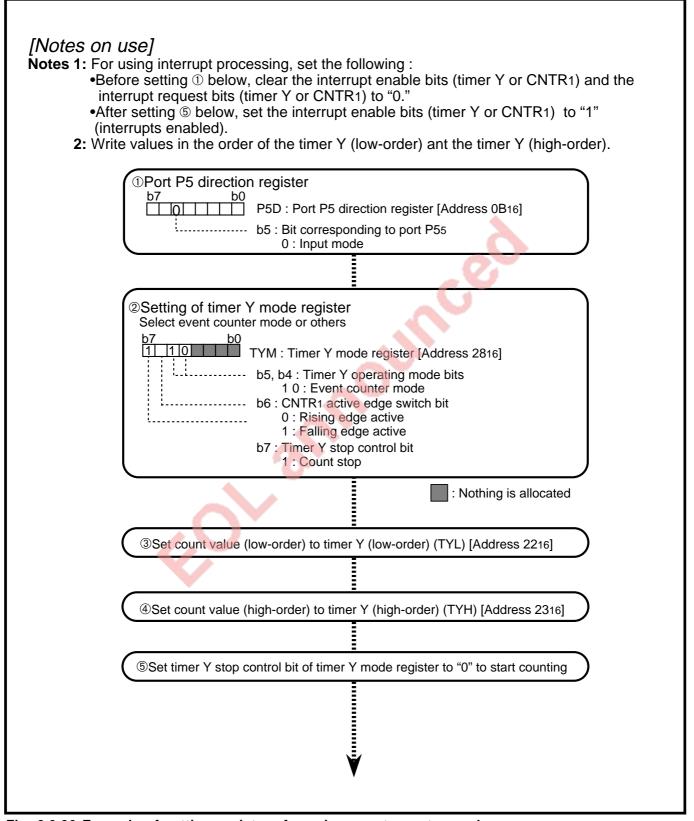

| Fig. 2.3.30 Example of setting registers for using event counter mode                           |       |

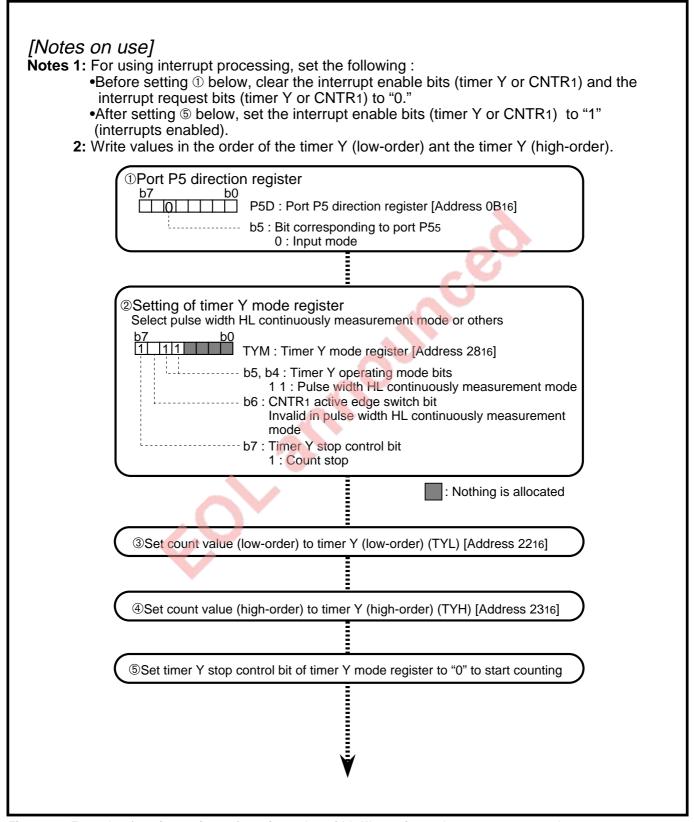

| Fig. 2.3.31 Example of setting registers for using pulse width HL continuously measurement mode |       |

| Fig. 2.3.32 Example of peripheral circuit                                                       |       |

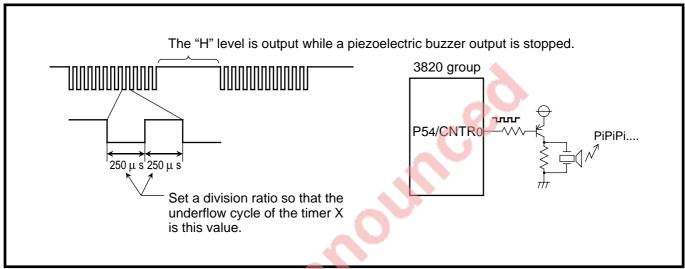

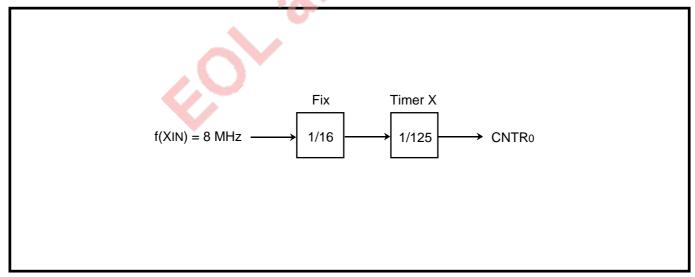

| Fig. 2.3.33 Connection of timer and setting of division ratio                                   |       |

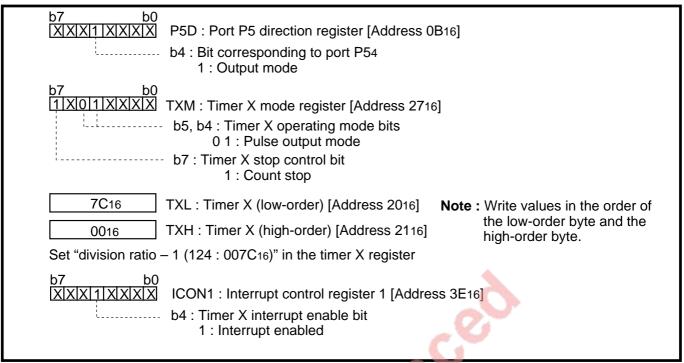

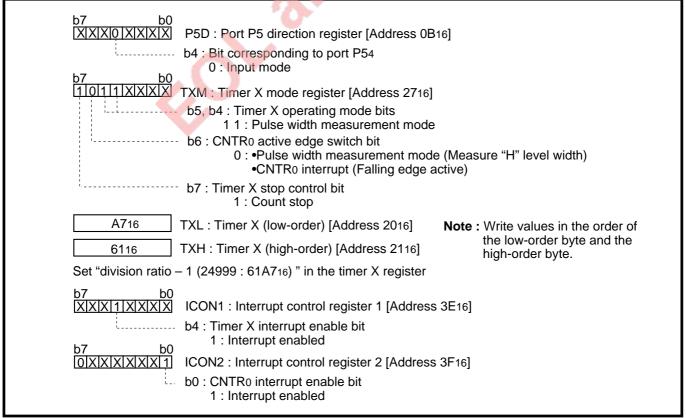

| Fig. 2.3.34 Setting of related registers                                                        |       |

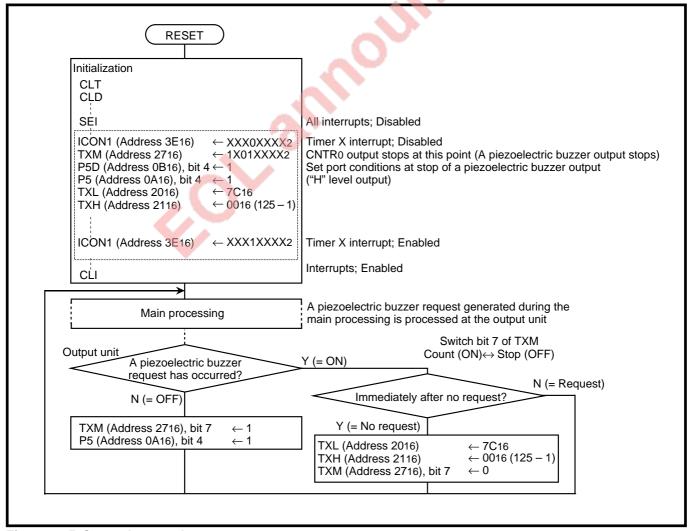

| Fig. 2.3.35 Control procedure                                                                   |       |

| Fig. 2.3.36 Example of peripheral circuit                                                       |       |

| Fig. 2.3.37 Setting of related registers                                                        |       |

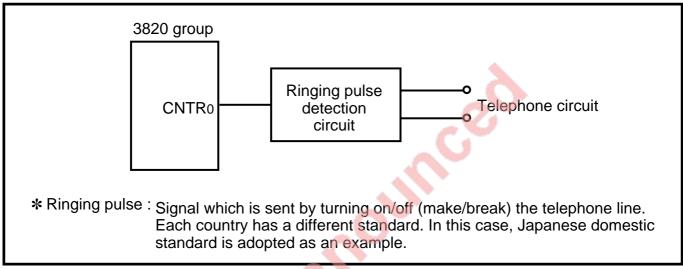

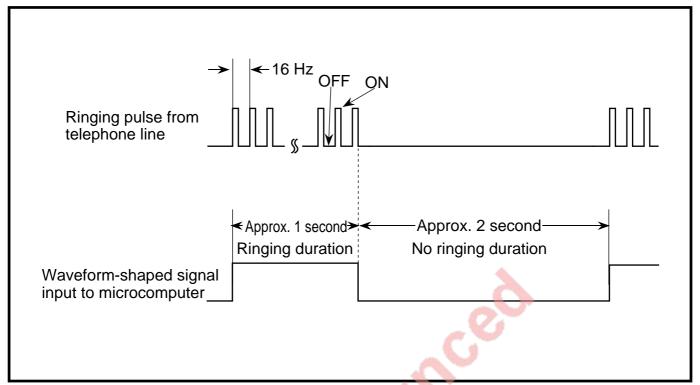

| Fig. 2.3.38 Ringer signal waveform                                                              |       |

|                                                                                                 |       |

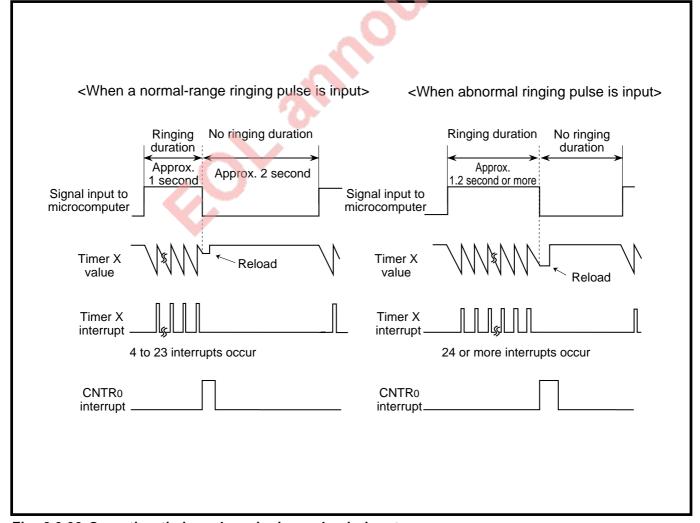

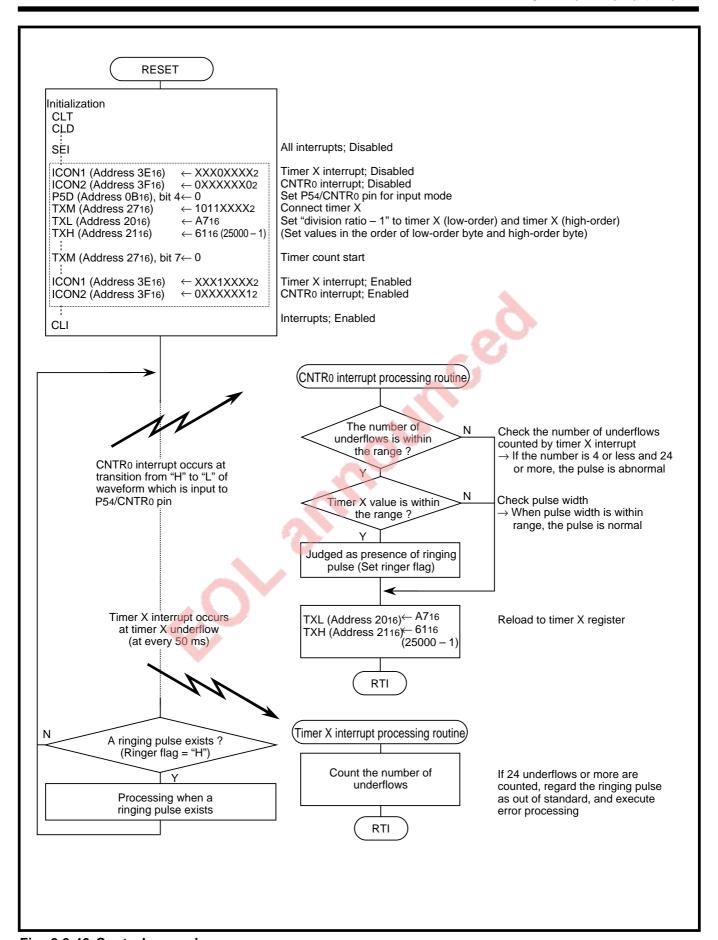

| Fig. 2.3.39 Operation timing when ringing pulse is input                                        |       |

| Fig. 2.3.44 Application connection example when DTD is used                                     |       |

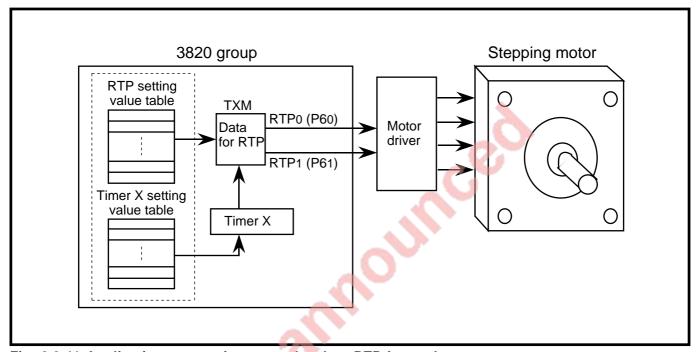

| Fig. 2.3.41 Application connection example when RTP is used                                     |       |

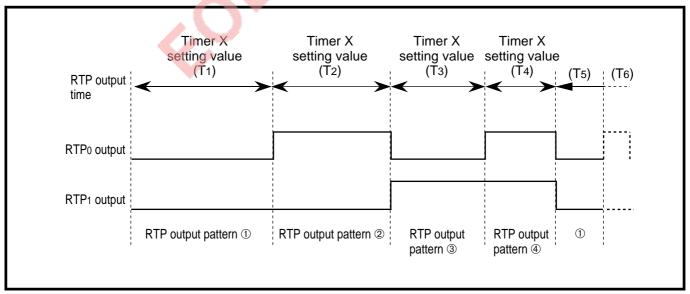

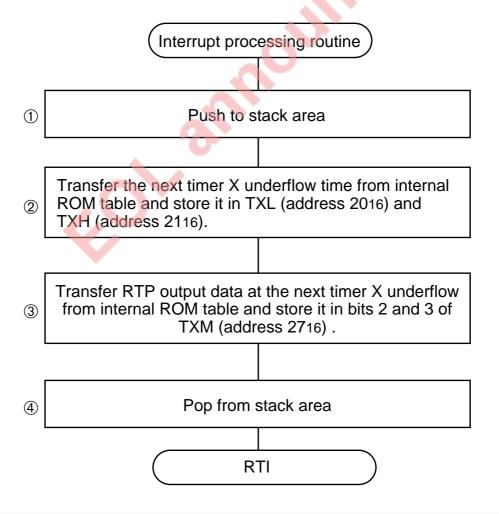

| Fig. 2.3.42 RTP output example                                                                  |       |

| Fig. 2.3.43 Timer X interrupt processing procedure example when RTP is used                     |       |

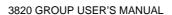

| Fig. 2.4.1 Timer mode operation example                                                         |       |

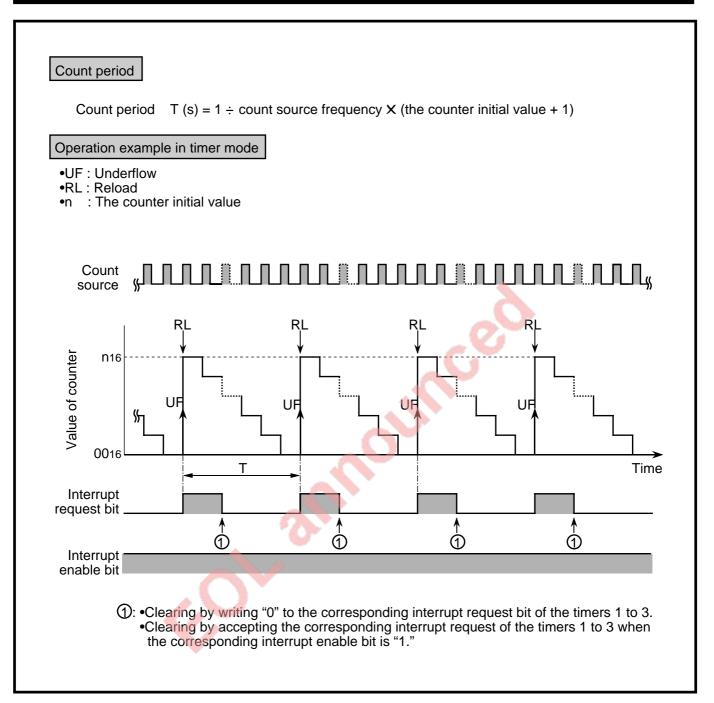

| Fig. 2.4.2 Rewriting example of counter and latch corresponding to timers 1 or 3                |       |

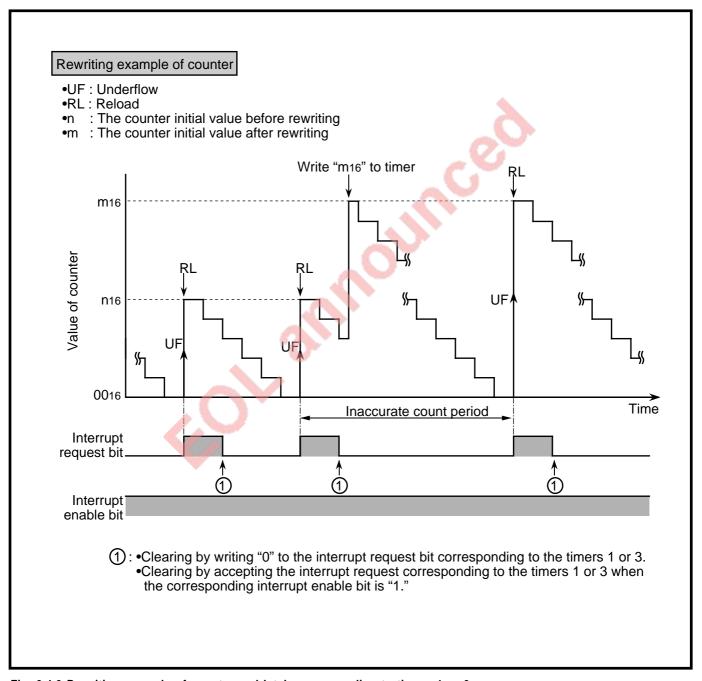

| Fig. 2.4.3 Rewriting example of timer 2 counter and timer 2 latch (Writing in timer 2 latch     |       |

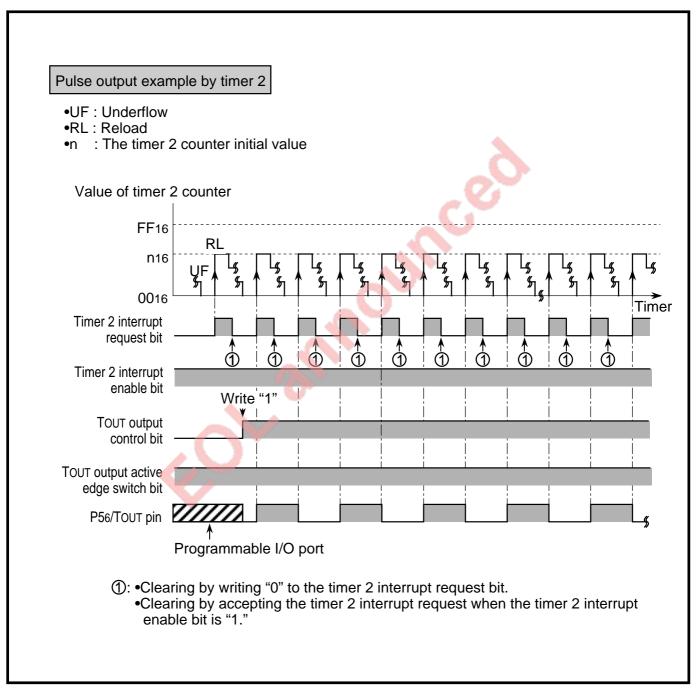

| Fig. 2.4.4 Pulse output example                                                                 |       |

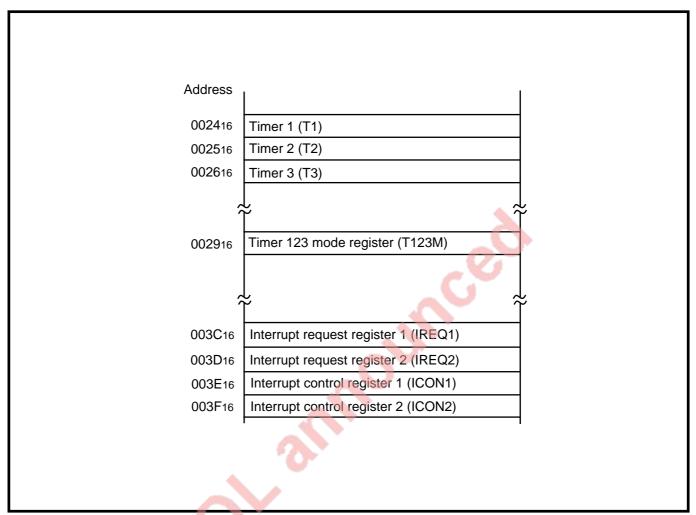

| Fig. 2.4.5 Memory allocation of timer-related registers                                         |       |

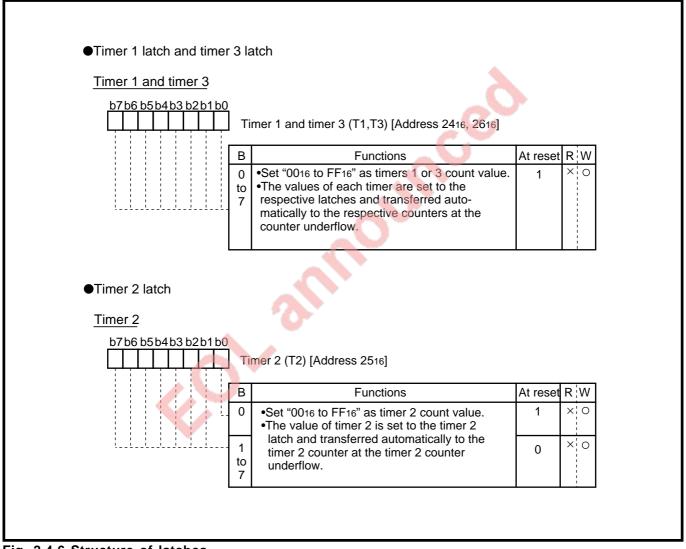

| Fig. 2.4.6 Structure of latches                                                                 |       |

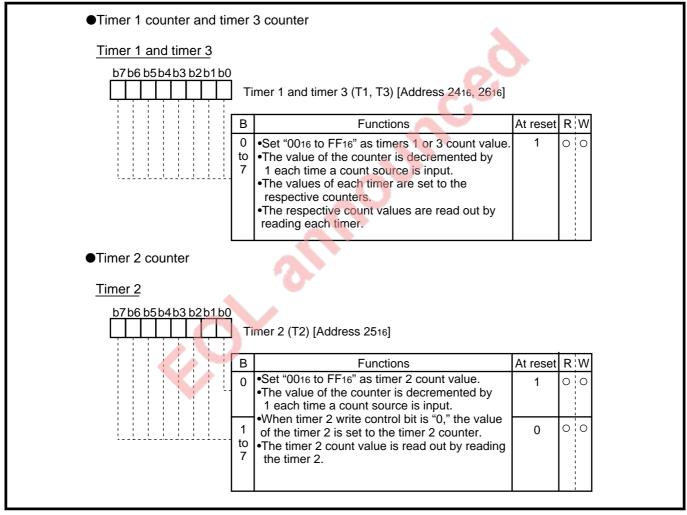

| Fig. 2.4.7 Structure of timer counters                                                          | 2-92  |

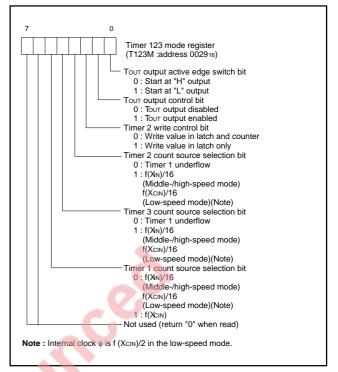

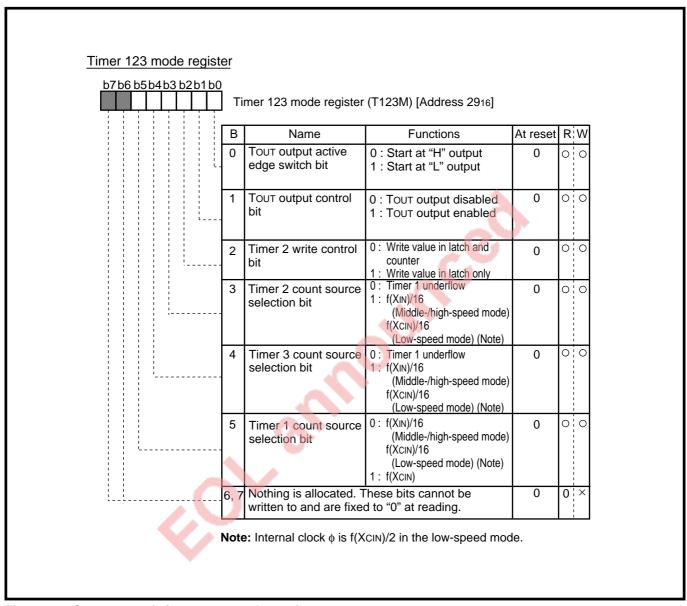

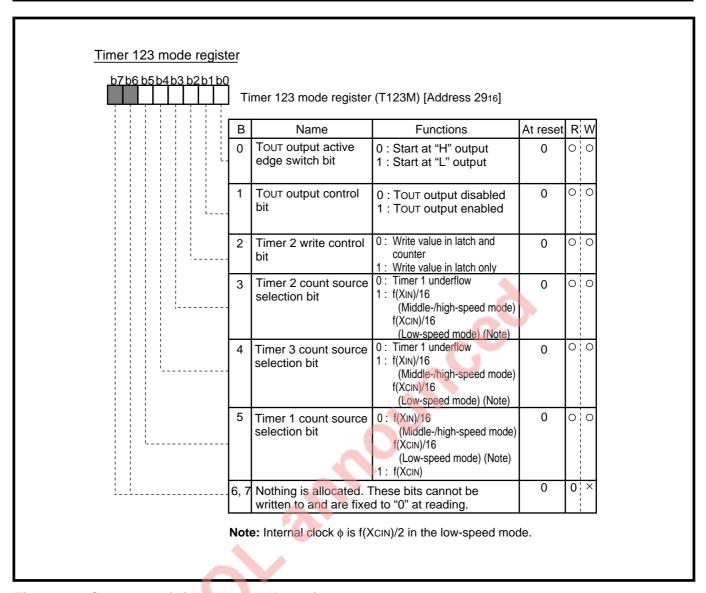

| Fig. 2.4.8 Structure of timer 123 mode register                                                 | 2-93  |

| Fig. 2.4.9 Structure of interrupt request register 1                                            | 2-95  |

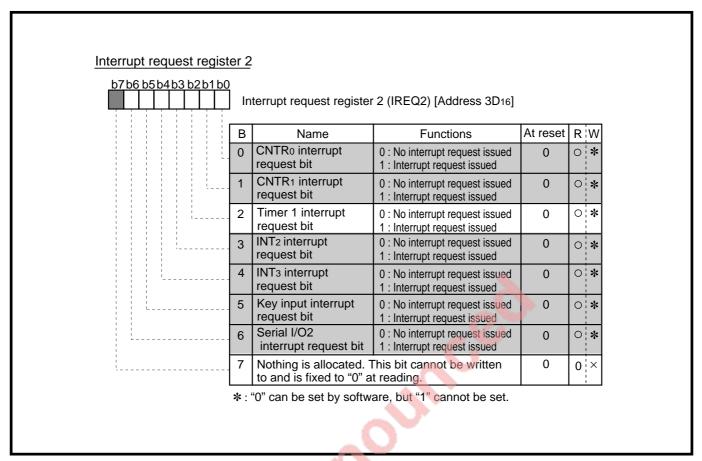

| Fig. 2.4.10 Structure of interrupt request register 2                                           | 2-96  |

| Fig. 2.4.11 Structure of interrupt control register 1                                           | 2-97  |

| Fig. 2.4.12 Structure of interrupt control register 2                                           | 2-98  |

| Fig. 2.4.13 Example of setting registers for timers 1, 2, and 3                                 | 2-99  |

| Fig. 2.4.14 Setting of related registers                                                        |       |

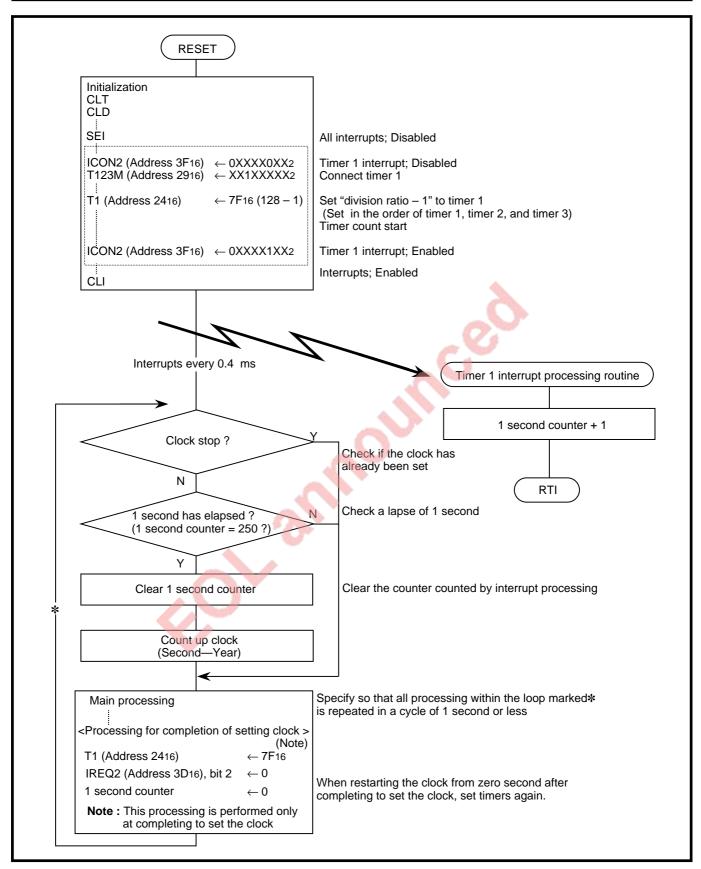

| Fig. 2.4.15 Control procedure                                                                   |       |

| Fig. 2.5.1 External connection example in clock synchronous mode                                |       |

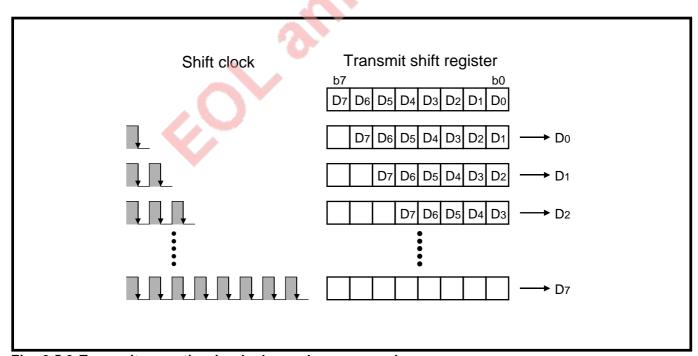

| Fig. 2.5.2 Shift clock                                                                          |       |

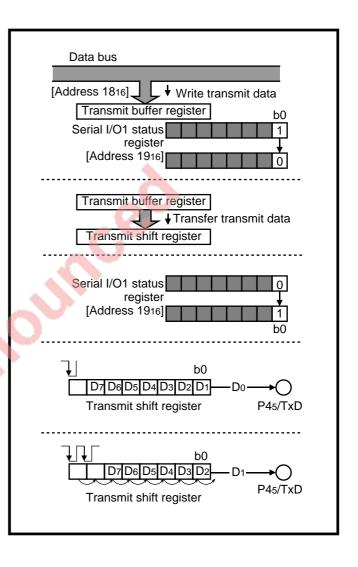

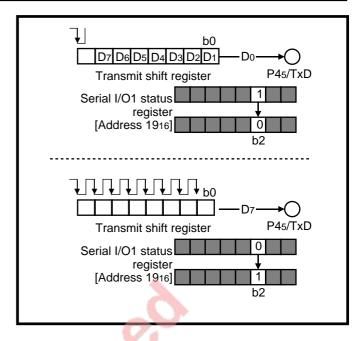

| Fig. 2.5.3 Transmit operation in clock synchronous mode                                         |       |

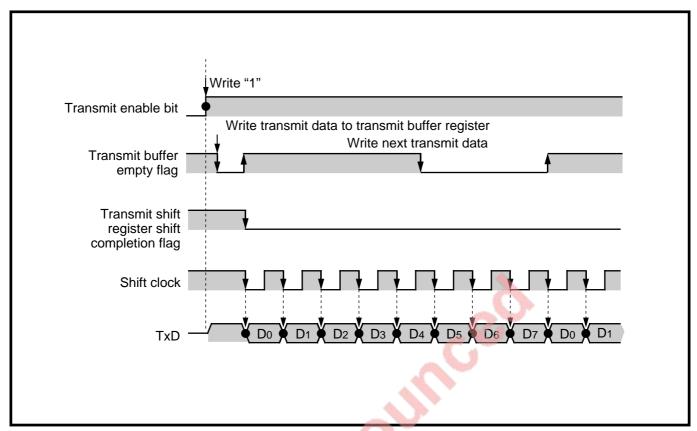

| Fig. 2.5.4 Transmit timing example in clock synchronous mode                                    |       |

| Fig. 2.5.5 Receive operation in clock synchronous mode                                          |       |

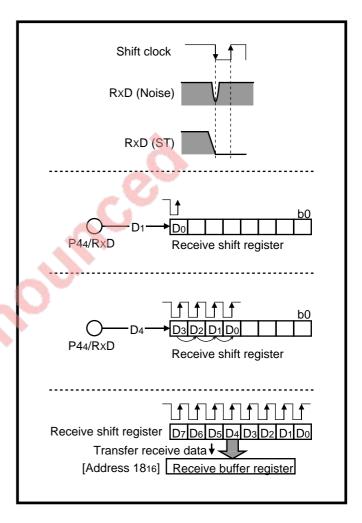

| Fig. 2.5.6 Receive timing example in clock synchronous mode                                     |       |

| Fig. 2.5.7 Transmit/receive timing example in clock synchronous mode                            |       |

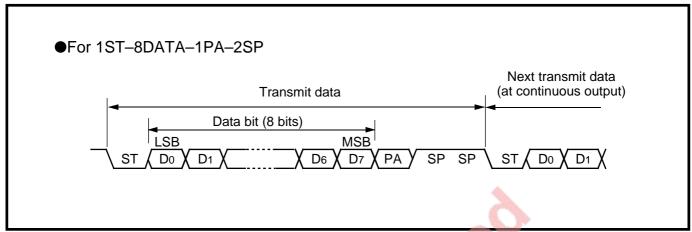

| Fig. 2.5.8 External connection example in UART mode                                             |       |

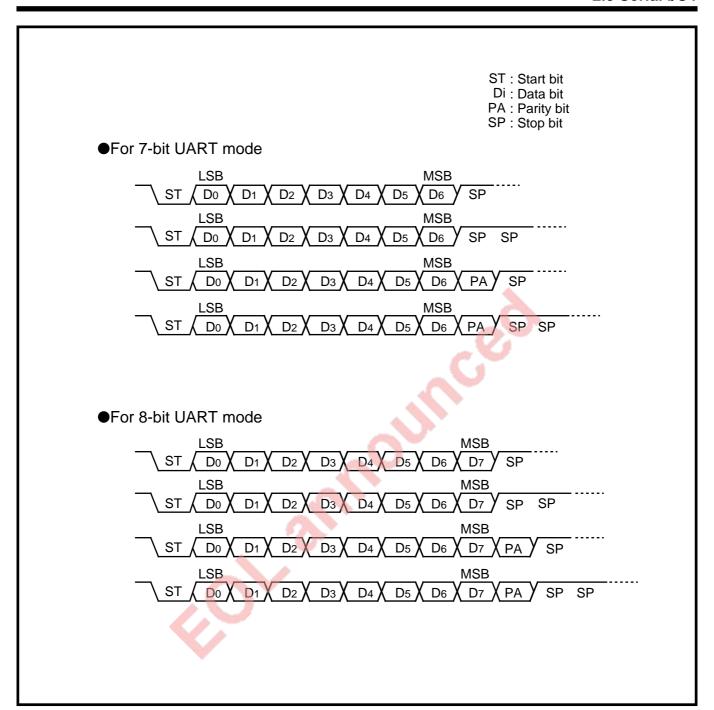

| Fig. 2.5.9 Transfer data format in UART mode                                                    |       |

| Fig. 2.5.10 All transfer data formats in UART mode                                              |       |

|                                                                                                 |       |

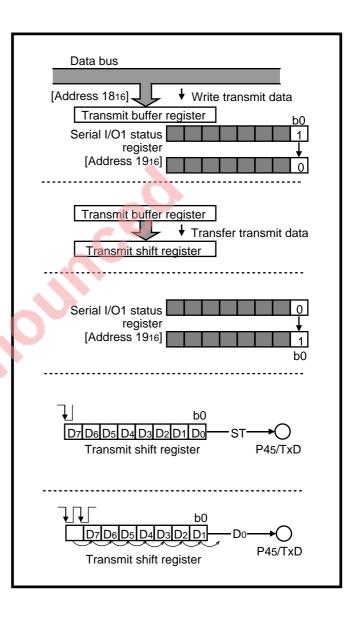

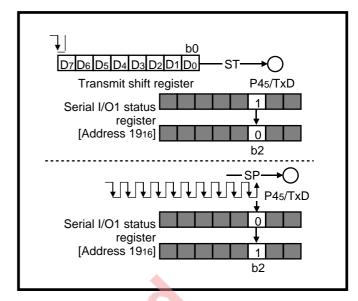

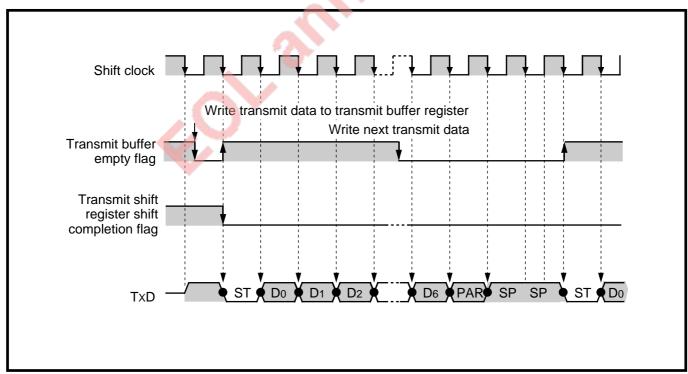

| Fig. 2.5.11 Transmit timing example in UART mode                                                |       |

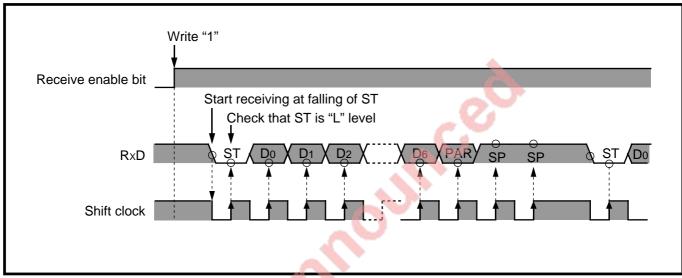

| Fig. 2.5.12 Receive timing example in UART mode                                                 |       |

| Fig. 2.5.13 Memory allocation of serial I/O1-related registers                                  |       |

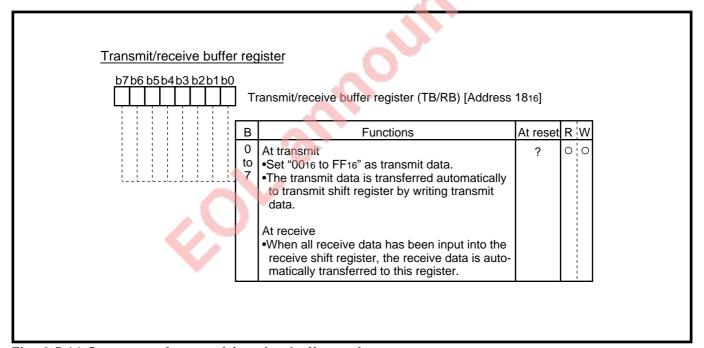

| Fig. 2.5.14 Structure of transmit/receive buffer register                                       |       |

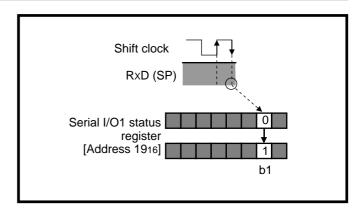

| Fig. 2.5.15 Structure of serial I/O1 status register                                            |       |

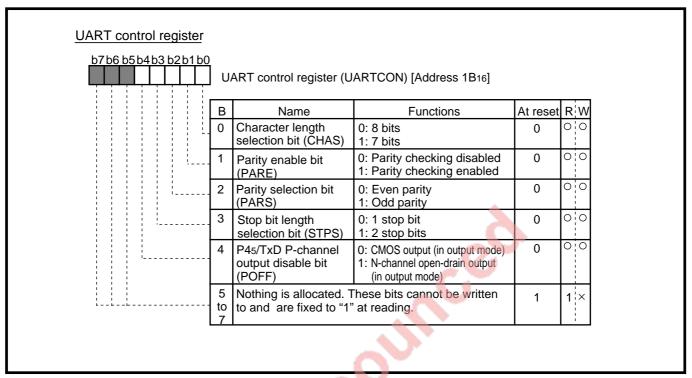

| Fig. 2.5.16 Structure of serial I/O1 control register                                           |       |

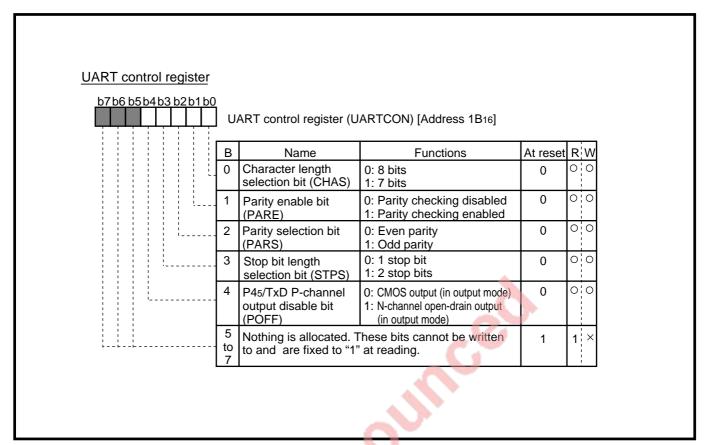

| Fig. 2.5.17 Structure of UART control register                                                  |       |

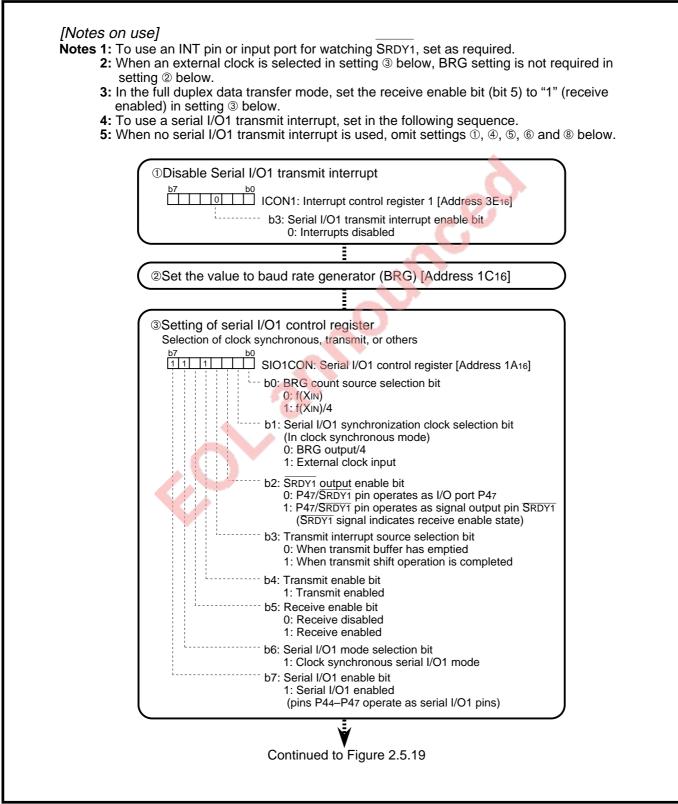

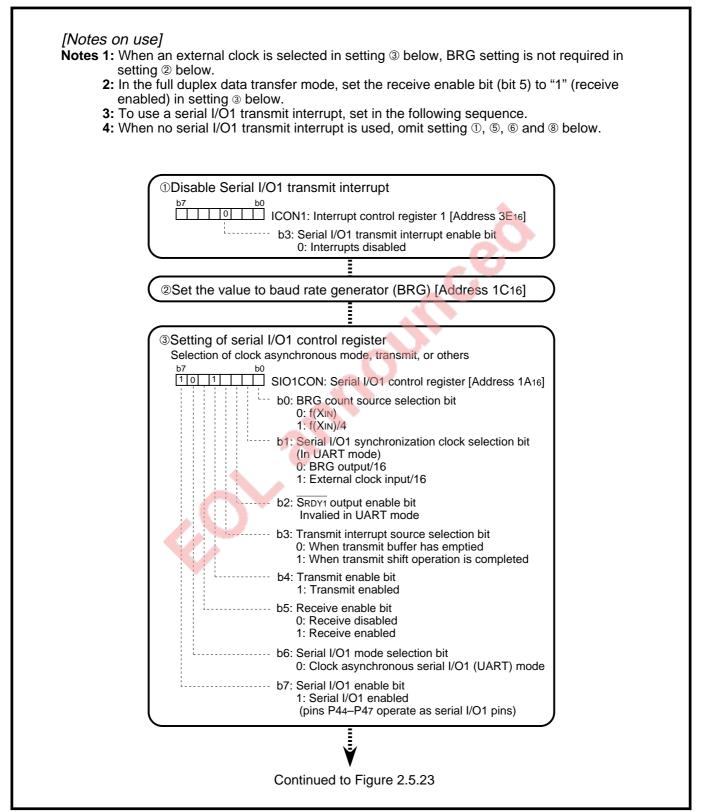

| Fig. 2.5.18 Transmitting method in clock synchronous mode (1)                                   |       |

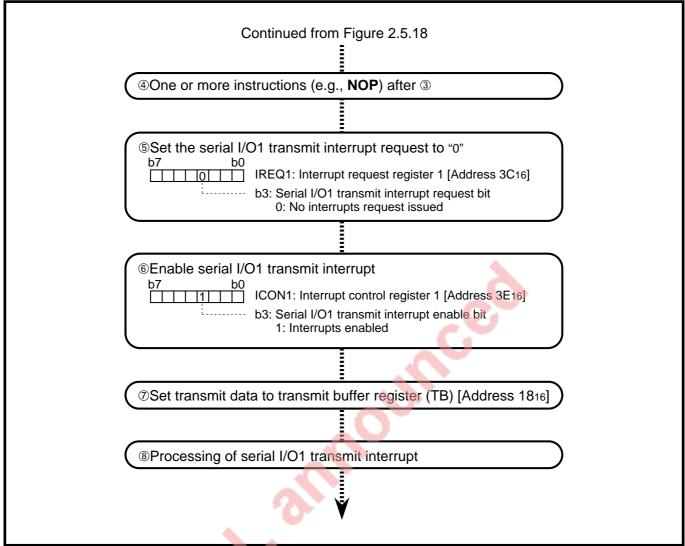

| Fig. 2.5.19 Transmitting method in clock synchronous mode (2)                                   |       |

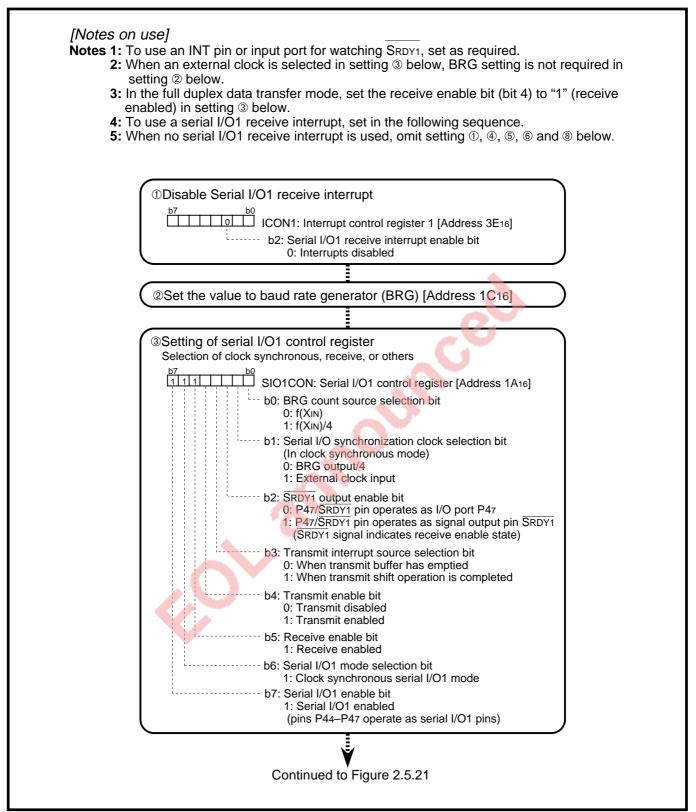

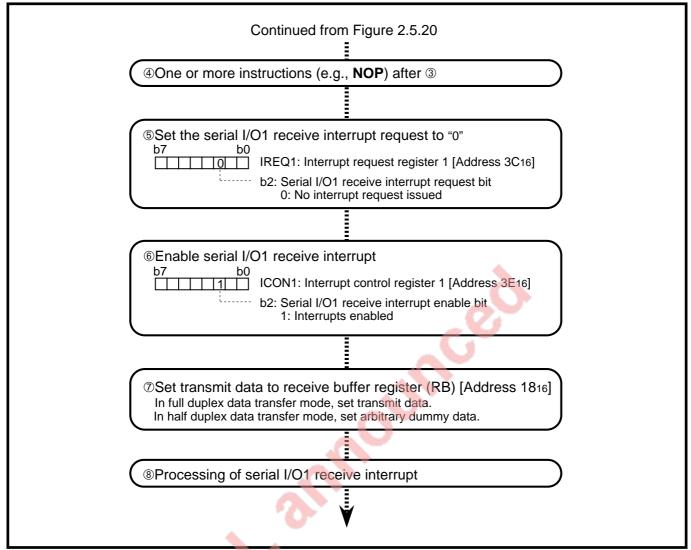

| Fig. 2.5.20 Receiving method in clock synchronous mode (1)                                      |       |

| Fig. 2.5.21 Receiving method in clock synchronous mode (2)                                      | 2-132 |

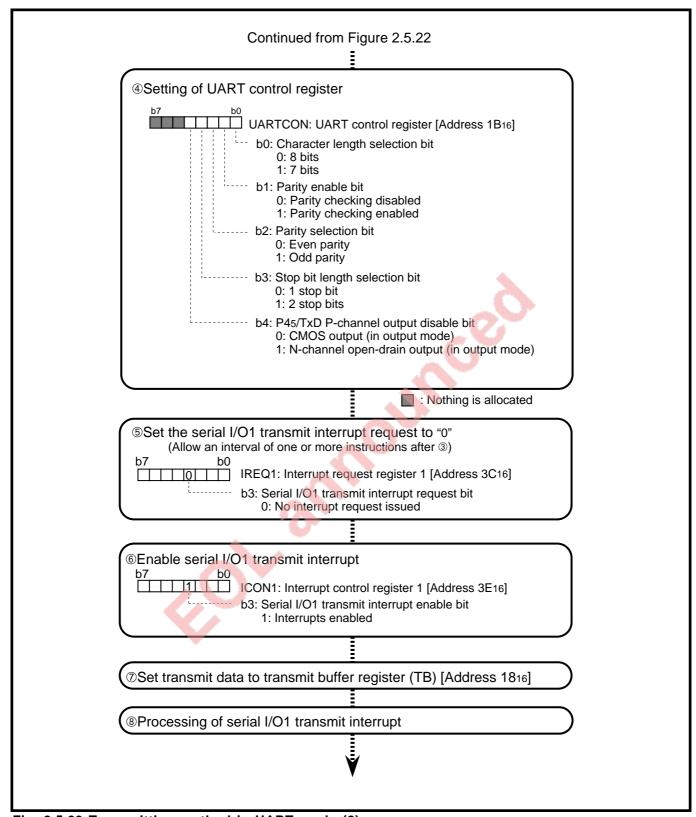

| Fig. | . 2.5.22 Transmitting method in UART mode (1)                                             | 2-133 |

|------|-------------------------------------------------------------------------------------------|-------|

| Fig. | . 2.5.23 Transmitting method in UART mode (2)                                             | 2-134 |

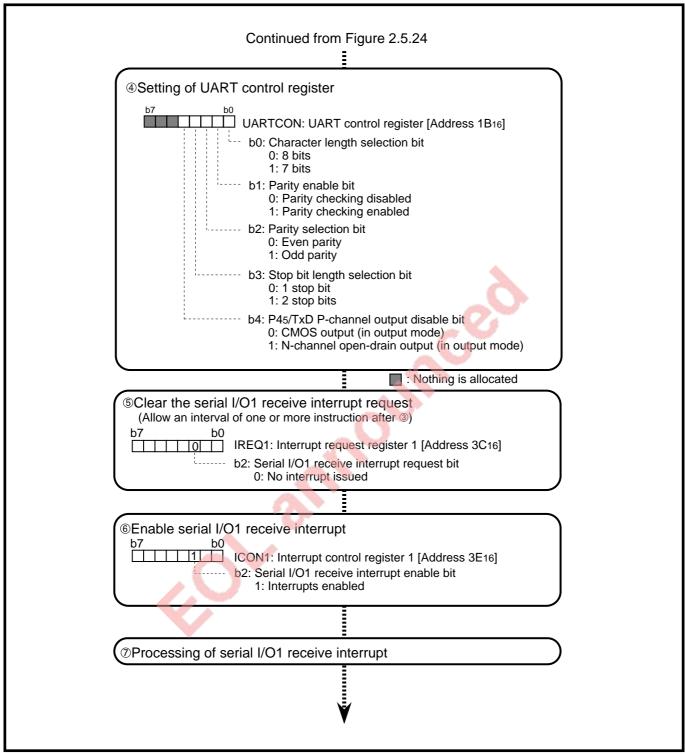

| Fig. | . 2.5.24 Receiving method in UART mode (1)                                                | 2-135 |

| Fig. | . 2.5.25 Receiving method in UART mode (2)                                                | 2-136 |

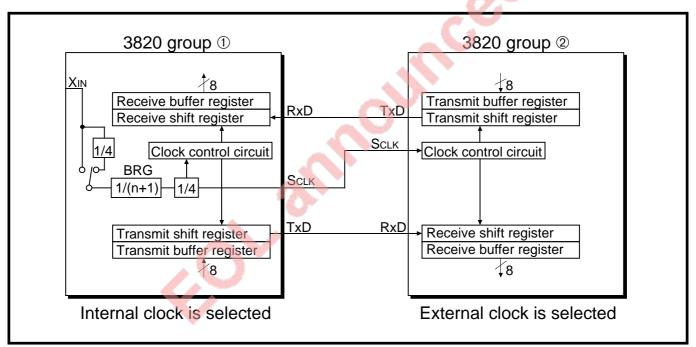

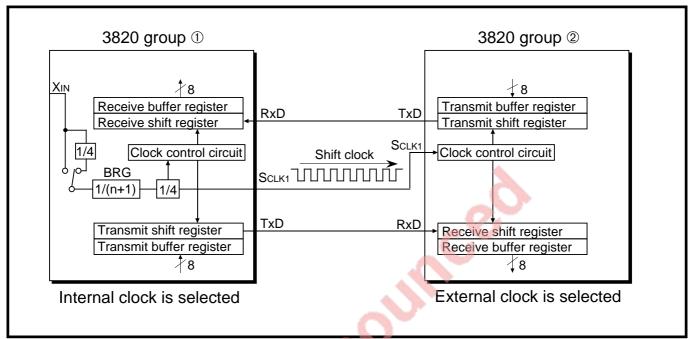

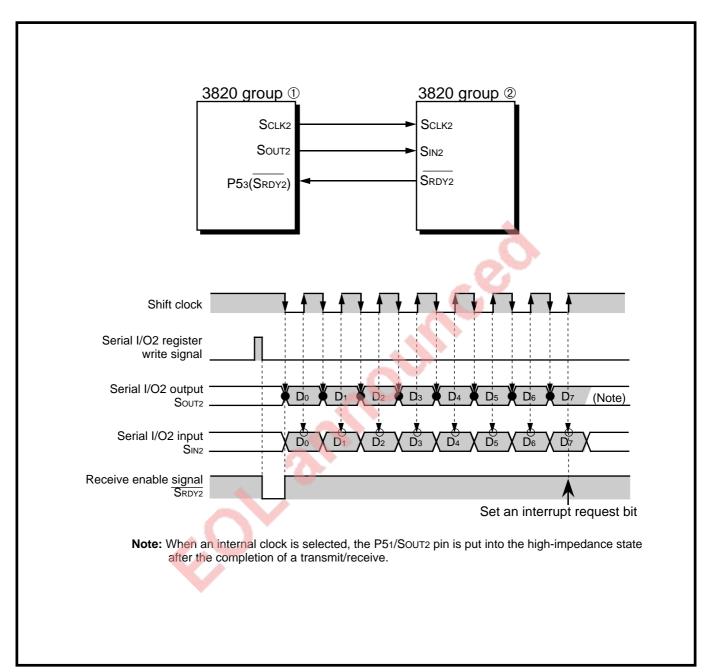

| Fig. | . 2.6.1 External connection example of serial I/O2                                        | 2-141 |

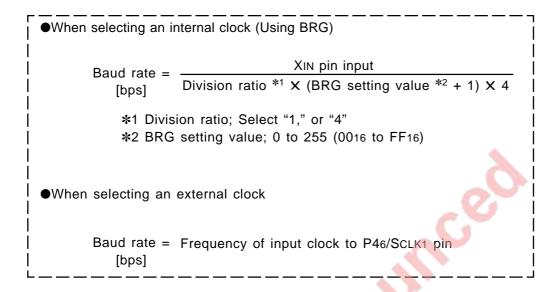

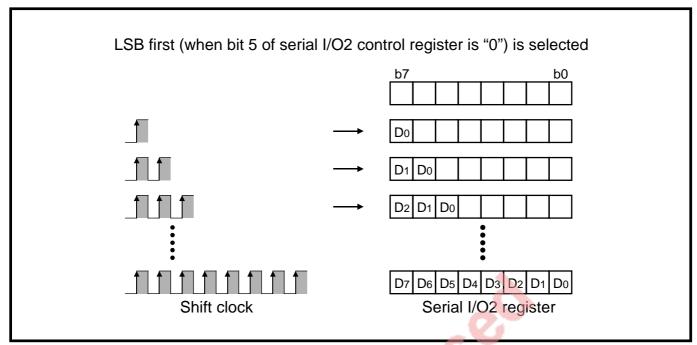

|      | . 2.6.2 Shift clock                                                                       |       |

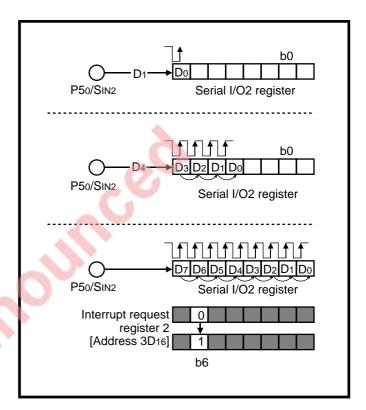

|      | . 2.6.3 Transmit operation of serial I/O2                                                 |       |

|      | . 2.6.4 Transmit timing example of serial I/O2                                            |       |

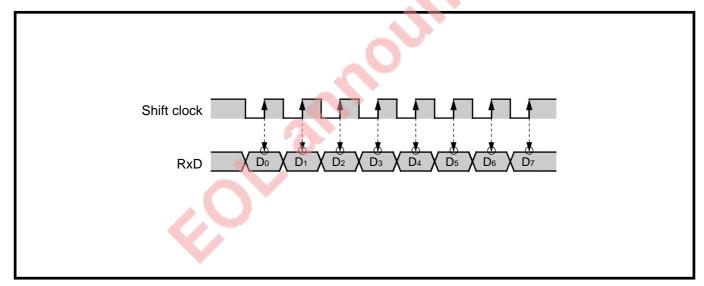

|      | . 2.6.5 Receive operation of serical I/O2                                                 |       |

|      | . 2.6.6 Receive timing example of serial I/O2                                             |       |

| Fig. | . 2.6.7 Transmit/receive timing example of serial I/O2 (P53/SRDY2 pin is used)            | 2-147 |

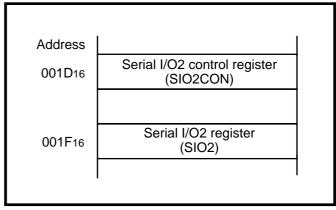

| Fig. | . 2.6.8 Memory allocation of serial I/O2-related registers                                | 2-149 |

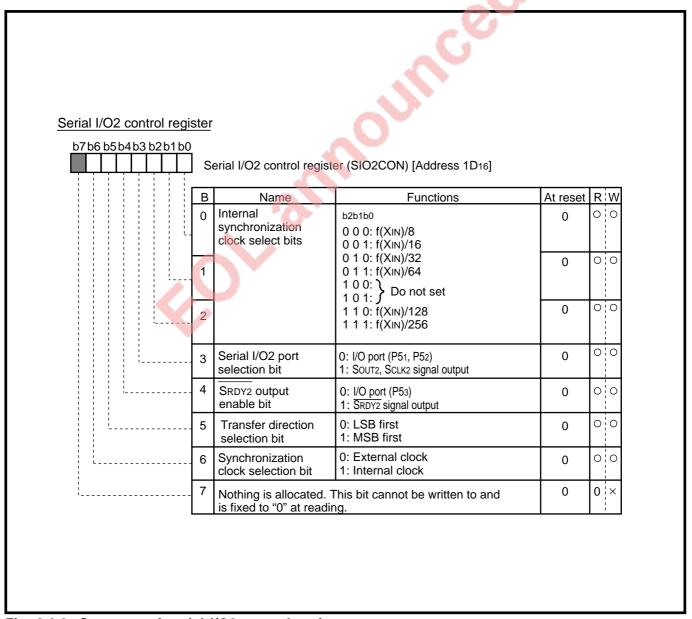

| _    | . 2.6.9 Structure of serial I/O2 control register                                         |       |

| _    | . 2.6.10 Structure of serial I/O2 register                                                |       |

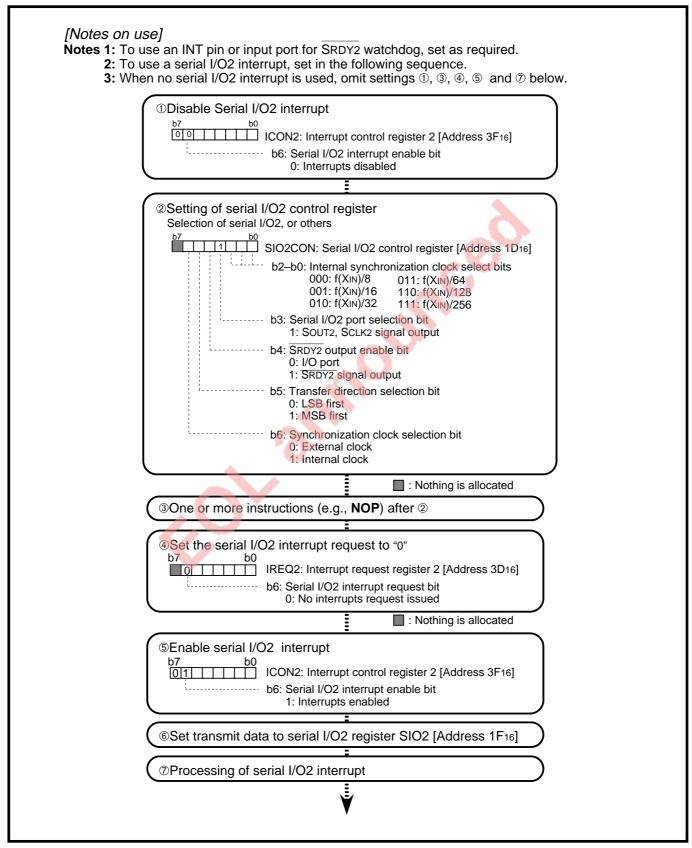

|      | . 2.6.11 Transmitting method of serial I/O2                                               |       |

|      | . 2.6.12 Receiving method of serial I/O2                                                  |       |

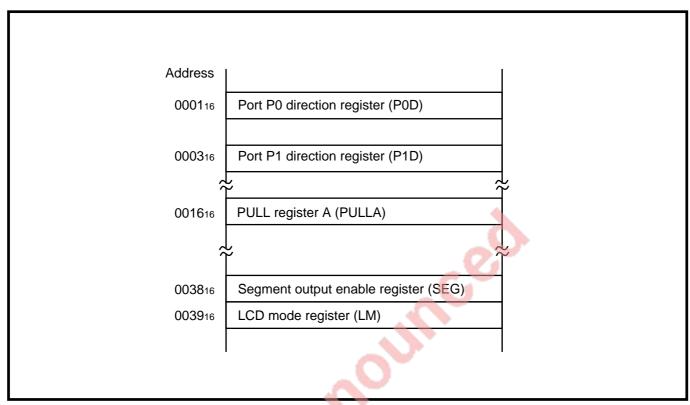

|      | . 2.7.1 Memory allocation of LCD display-related registers                                |       |

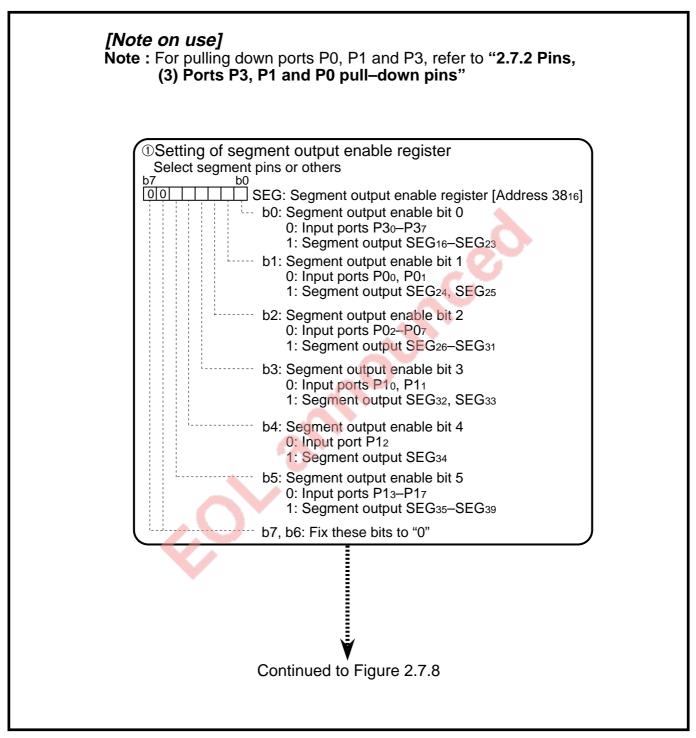

|      | . 2.7.2 Structure of segment output enable register                                       |       |

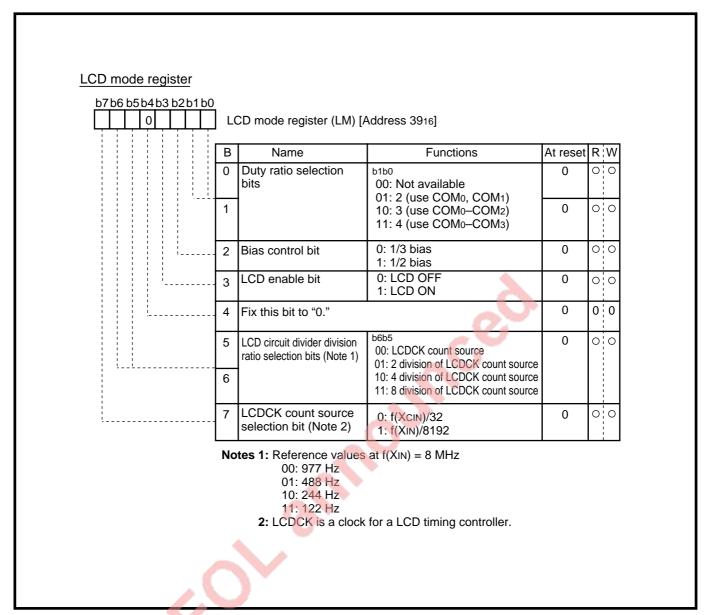

|      | 2.7.3 Structure of LCD mode register                                                      |       |

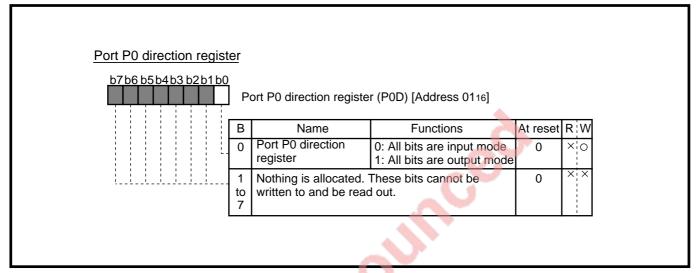

|      | . 2.7.4 Structure of port P0 direction register                                           |       |

|      | 2.7.5 Structure of port P1 direction register                                             |       |

|      | 2.7.6 Structure of PULL register A                                                        |       |

|      | 2.7.7 Example of setting registers for LCD display (1)                                    |       |

|      | . 2.7.8 Example of setting registers for LCD display (2)                                  |       |

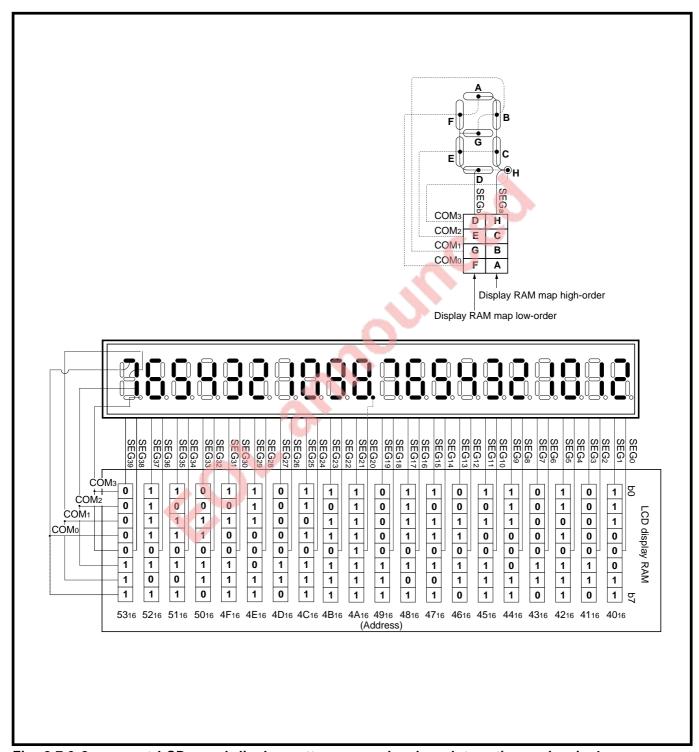

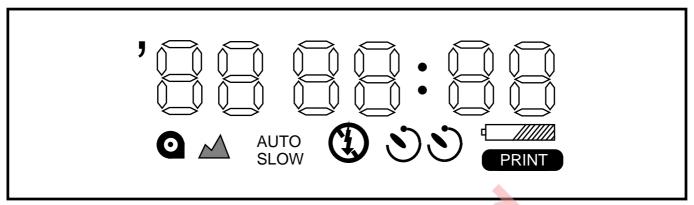

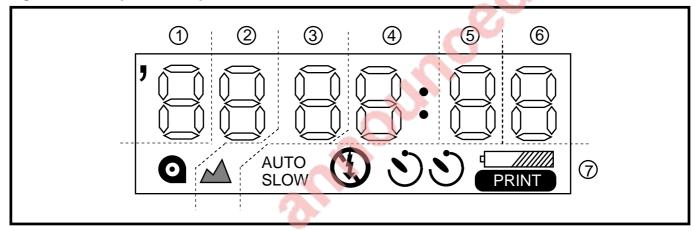

|      | . 2.7.9 8-segment LCD panel display pattern example when the duty ratio number is 4       |       |

|      | . 2.7.10 LCD panel example                                                                |       |

|      | . 2.7.11 Segment allocation example                                                       |       |

|      | . 2.7.12 LCD display RAM setting example                                                  |       |

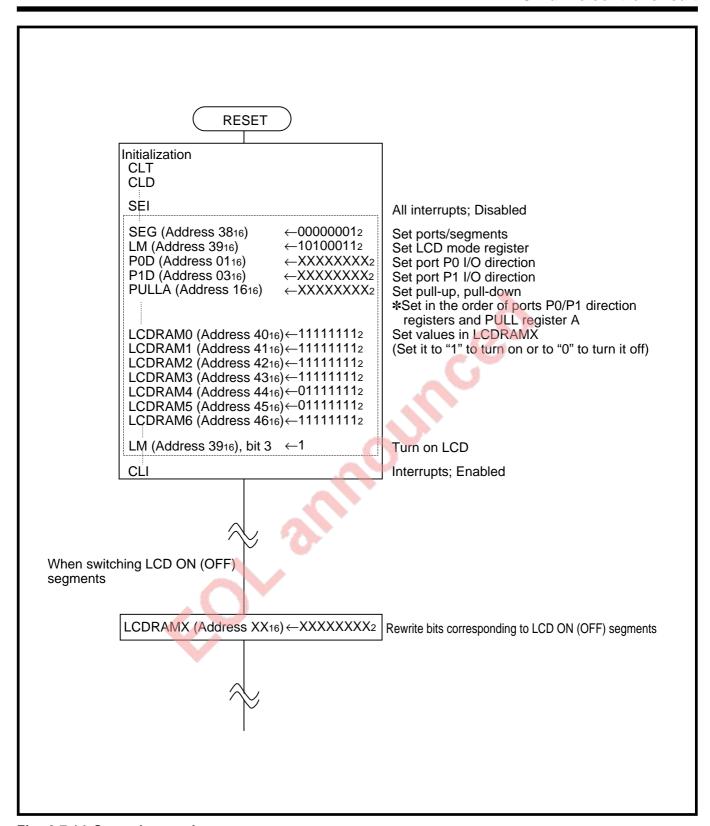

|      | . 2.7.13 Setting of related registers                                                     |       |

|      | 2.7.14 Control procedure                                                                  |       |

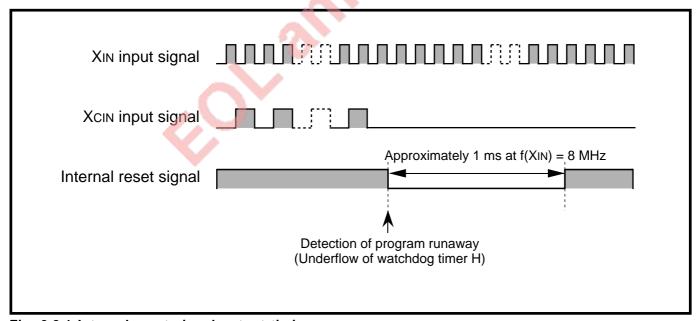

| _    | . 2.8.1 Internal reset signal output timing                                               |       |

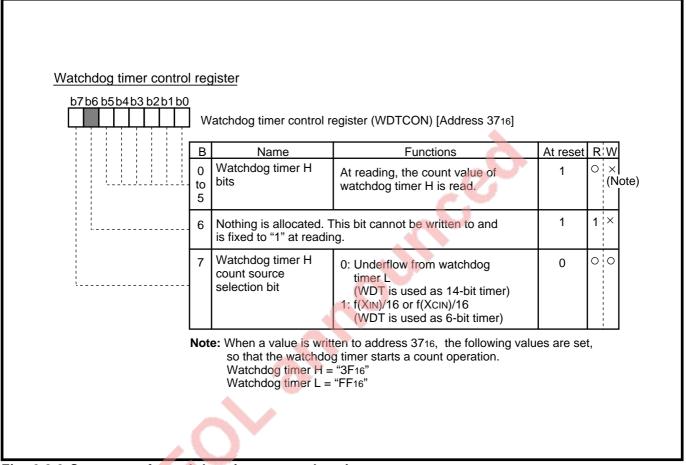

|      | . 2.8.2 Structure of watchdog timer control register                                      |       |

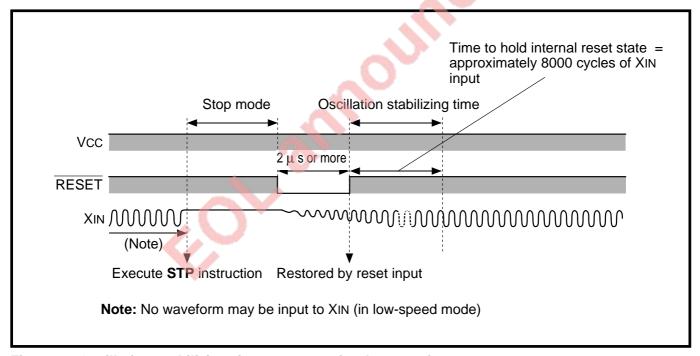

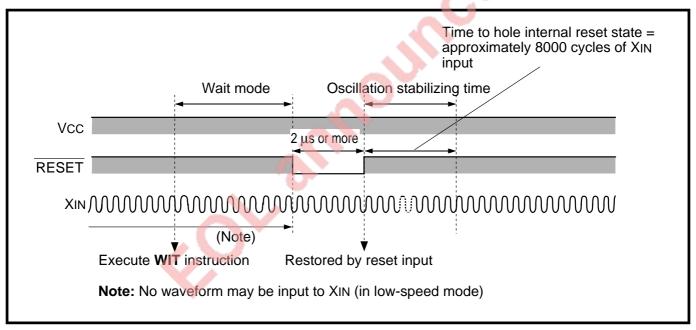

|      | . 2.9.1 Oscillation stabilizing time at restoration by reset input                        |       |

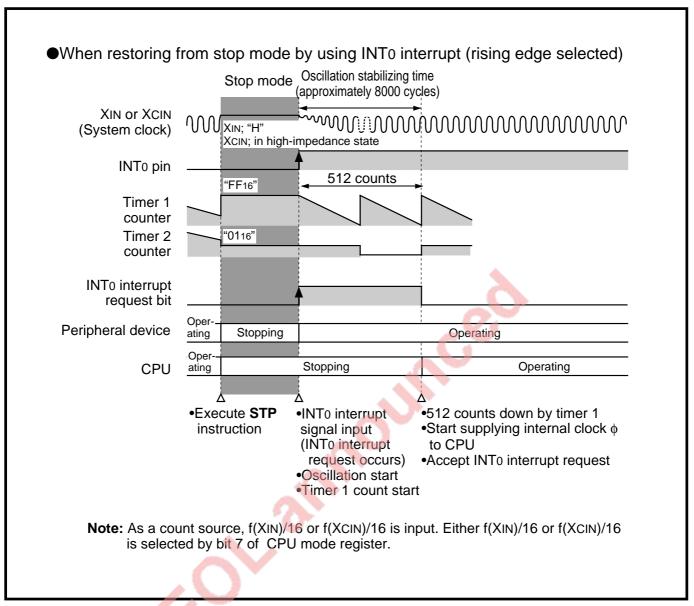

|      | . 2.9.2 Execution sequence example at restoration by occurrence of INTo interrupt request |       |

|      | . 2.9.3 Reset input time                                                                  |       |

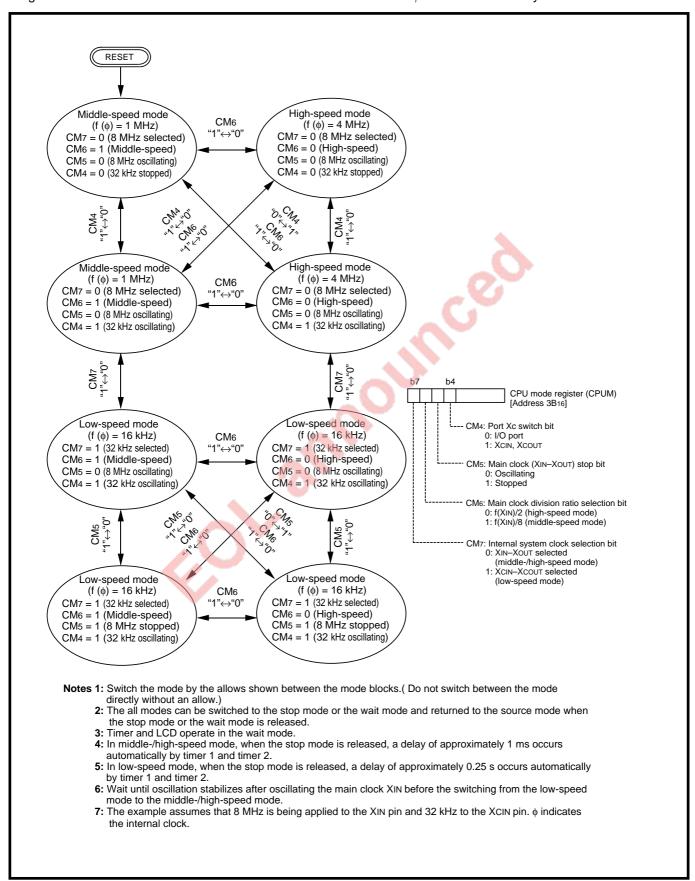

|      | . 2.9.4 State transitions of internal clock φ                                             |       |

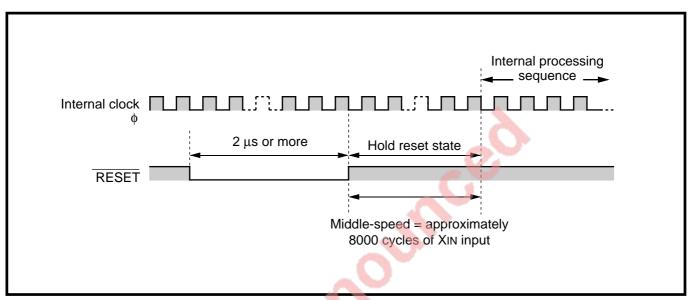

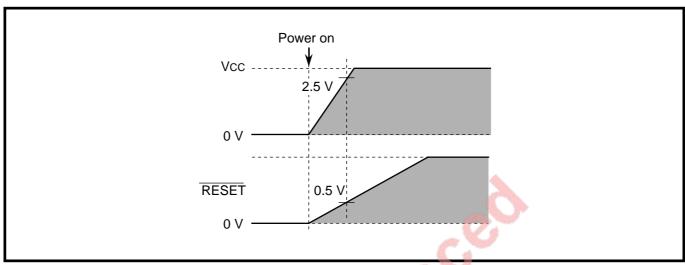

| _    | . 2.10.1 Internal reset state hold/release timing                                         |       |

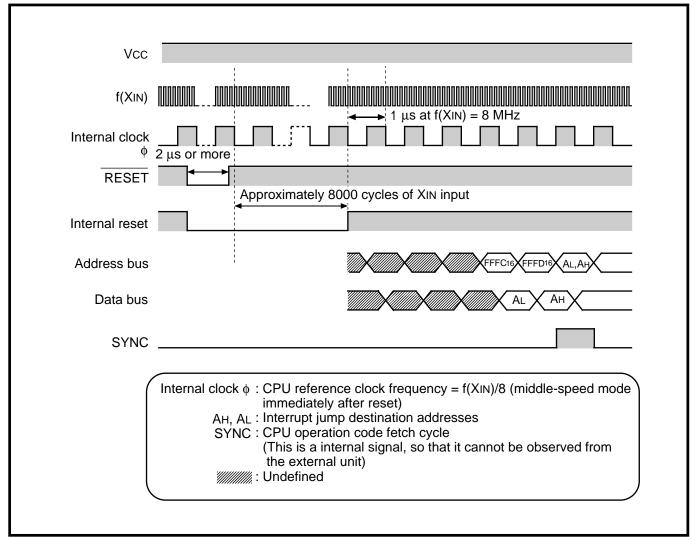

|      | . 2.10.2 Internal processing sequence immediately after reset release                     |       |

|      | . 2.10.3 Internal state of microcomputer immediately after reset release                  |       |

|      | 2.10.4 Poweron reset conditions                                                           |       |

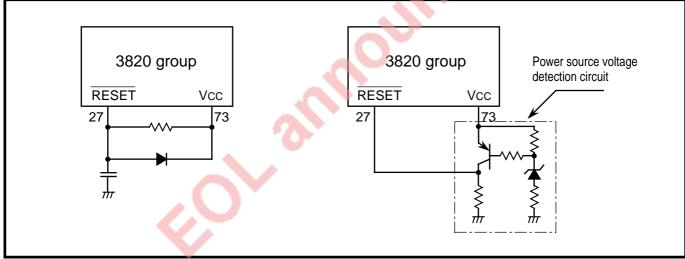

|      | . 2.10.5 Poweron reset circuit examples                                                   |       |

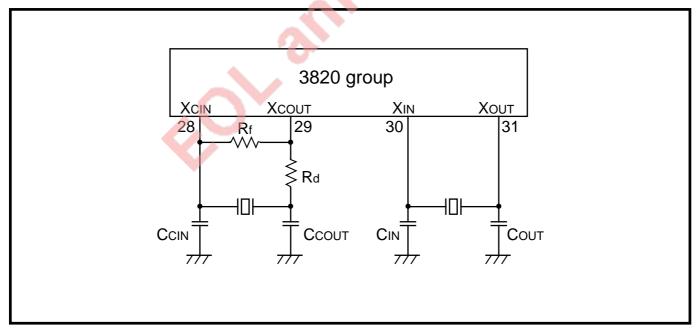

|      | . 2.11.1 Oscillation circuit example using ceramic resonators                             |       |

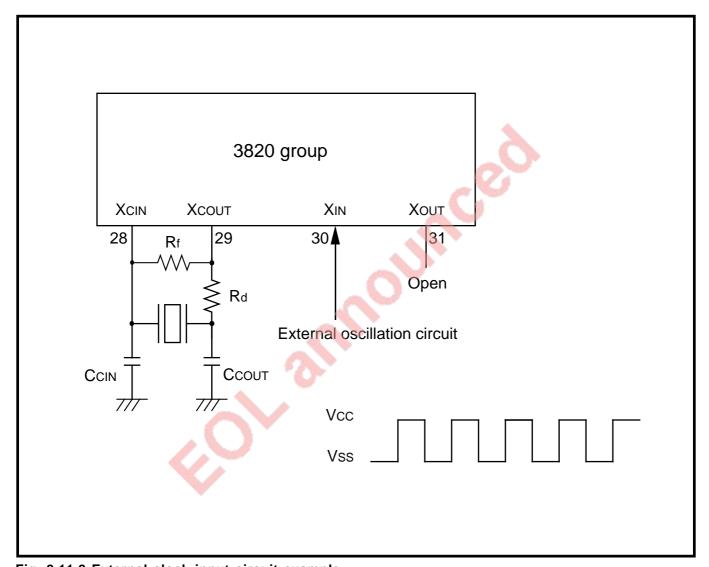

|      | . 2.11.2 External clock input circuit example                                             |       |

|      | . 2.11.3 Clock generating circuit block diagram                                           |       |

|      | . 2.11.4 Structure of φ output control register                                           |       |

|      | . 2.11.5 State transitions of internal clock φ                                            |       |

|      | 2.11.6 Oscillation stabilizing time at poweron                                            |       |

|      | . 2.11.7 Oscillation stabilizing time at reoscillation of XIN                             |       |

|      |                                                                                           |       |

### CHAPTER 3. APPENDIX

| Fig. 3 | s.1.1 Pin configuration of EPROM version (top view)                       | 3-5  |

|--------|---------------------------------------------------------------------------|------|

| Fig. 3 | 1.1.2 Pin configuration of One Time PROM version (top view) (1)(1)        | 3-6  |

| Fig. 3 | 1.3 Pin configuration of One Time PROM version (top view) (2)(2)          | 3-7  |

| Fig. 3 | 1.1.4 Functional block diagram of built-in PROM version                   | 3-8  |

| Fig. 3 | 1.1.5 Programming and testing of One Time PROM version (shipped in blank) | 3-10 |

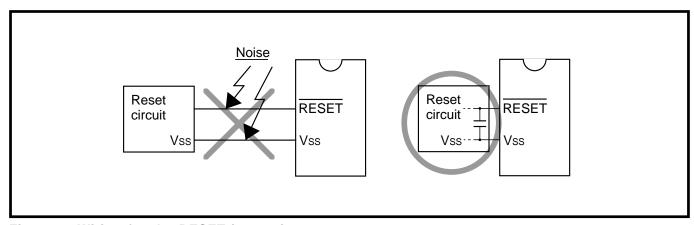

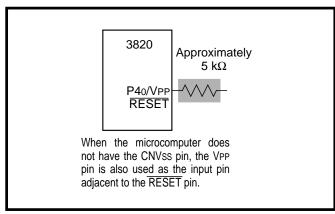

| Fig. 3 | 2.1 Wiring for the RESET input pin                                        | 3-11 |

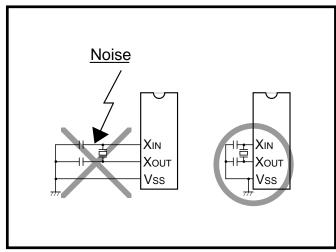

|        | 2.2 Wiring for clock I/O pins                                             |      |

| Fig. 3 | 2.3 Wiring for the VPP pin of the One Time PROM and the EPROM version     | 3-12 |

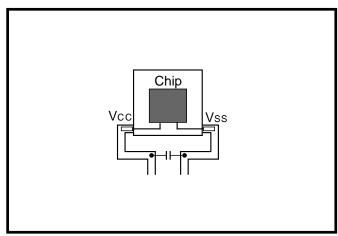

| Fig. 3 | 2.4 Bypass capacitor across the Vss line and the Vcc line                 | 3-12 |

| Fig. 3 | 2.5 Analog signal line and a resistor and a capacitor                     | 3-13 |

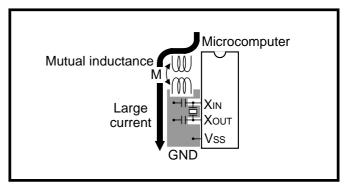

| Fig. 3 | 2.6 Wiring for a large current signal line                                | 3-13 |

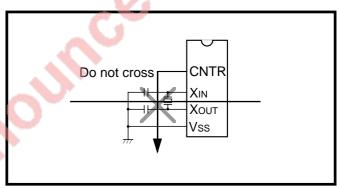

| Fig. 3 | 2.7 Wiring to a signal line where potential levels change frequently      | 3-14 |

| Fig. 3 | 2.8 Vss pattern on the underside of an oscillator                         | 3-14 |

|        | 2.9 Setup for I/O ports                                                   |      |

| Fig. 3 | 3.2.10 Watchdog timer by software                                         | 3-15 |

| Fig. 3 | 3.1 Structure of port P0 and P1 direction registers                       | 3-16 |

| Fig. 3 | 3.2 Structure of port Pi (i = 2, 4 to 7) direction registers              | 3-16 |

| Fig. 3 | 3.3 Structure of PULL register A                                          | 3-17 |

| Fig. 3 | 3.4 Structure of PULL register B                                          | 3-17 |

| Fig. 3 | 3.5 Structure of serial I/O1 status register                              | 3-18 |

|        | 3.6 Structure of serial I/O1 control register                             |      |

| Fig. 3 | 3.7 Structure of UART control register                                    | 3-20 |

| Fig. 3 | 3.8 Structure of serial I/O2 control register                             | 3-20 |

| Fig. 3 | 3.9 Structure of timer X mode register                                    | 3-21 |

| Fig. 3 | 3.10 Structure of timer Y mode register                                   | 3-22 |

| Fig. 3 | 3.3.11 Structure of timer 123 mode register                               | 3-23 |

|        | 3.12 Structure of φ output control register                               |      |

| Fig. 3 | 3.13 Structure of watchdog timer control register                         | 3-24 |

| Fig. 3 | 3.14 Structure of segment output register                                 | 3-24 |

| Fig. 3 | 3.15 Structure of LCD mode register                                       | 3-25 |

| Fig. 3 | 3.16 Structure of interrupt edge selection register                       | 3-26 |